- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385388 > HMP8190CN (HARRIS SEMICONDUCTOR) NTSC/PAL Video Encoder PDF資料下載

參數(shù)資料

| 型號: | HMP8190CN |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | NTSC/PAL Video Encoder |

| 中文描述: | COLOR SIGNAL ENCODER, PQFP64 |

| 文件頁數(shù): | 21/32頁 |

| 文件大小: | 227K |

| 代理商: | HMP8190CN |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當(dāng)前第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

21

1

FIELD Detect

Select

This bit specifies whether an odd or even field is starting when the leading edge of HSYNC

occurs within the FIELD Detect Window. It is ignored unless HSYNC and VSYNC are config-

ured as inputs.

0 = odd field

1 = even field

0

B

0

Field Detect

Window Size High

This bit is cascaded with Field Detect Window Size Low to form a 9-bit Field Detect Window Size

value. This bit is ignored unless HSYNC and VSYNC are configured as inputs.

0

B

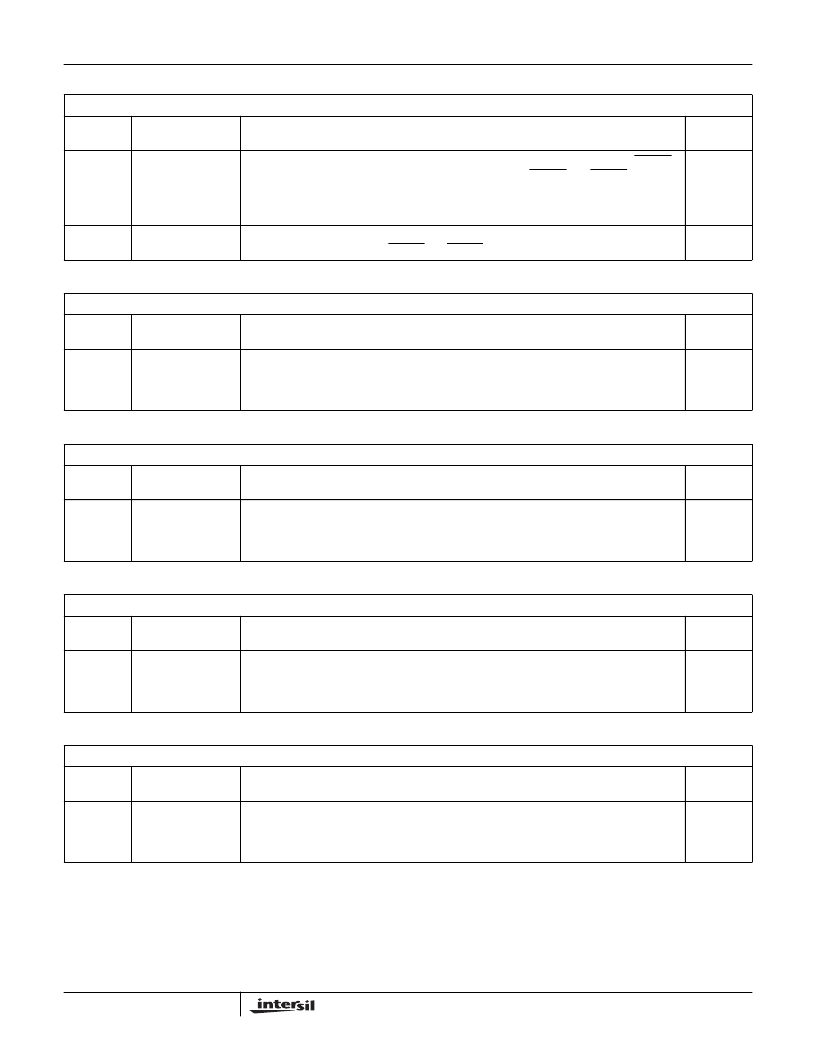

TABLE 39. FIELD CONTROL REGISTER 2

SUB ADDRESS = 27

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

TABLE 40. PHASE INCREMENT REGISTER 0

SUB ADDRESS = 6B

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7-0

PHINC 0

(LSB)

The 8-bit registers PHINC 0–3 are cascaded together to form a 32-bit PHINC value. The

PHINC value is the phase increment value of the color subcarrier generation NCO. When the

BT.656 ancillary data is selected as the PHINC source, the PHINC registers may be read to

determine the last PHINC value loaded via the selected interface.

00

H

TABLE 41. PHASE INCREMENT REGISTER 1

SUB ADDRESS = 6C

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7-0

PHINC 1

The 8-bit registers PHINC 0–3 are cascaded together to form a 32-bit PHINC value. The

PHINC value is the phase increment value of the color subcarrier generation NCO. When the

BT.656 ancillary data is selected as the PHINC source, the PHINC registers may be read to

determine the last PHINC value loaded via the selected interface.

00

H

TABLE 42. PHASE INCREMENT REGISTER 2

SUB ADDRESS = 6D

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7-0

PHINC 2

The 8-bit registers PHINC 0–3 are cascaded together to form a 32-bit PHINC value. The

PHINC value is the phase increment value of the color subcarrier generation NCO. When the

BT.656 ancillary data is selected as the PHINC source, the PHINC registers may be read to

determine the last PHINC value loaded via the selected interface.

00

H

TABLE 43. PHASE INCREMENT REGISTER 1

SUB ADDRESS = 6E

H

BIT

NUMBER

FUNCTION

DESCRIPTION

RESET

STATE

7-0

PHINC 3

(MSB)

The 8-bit registers PHINC 0–3 are cascaded together to form a 32-bit PHINC value. The

PHINC value is the phase increment value of the color subcarrier generation NCO. When the

BT.656 ancillary data is selected as the PHINC source, the PHINC registers may be read to

determine the last PHINC value loaded via the selected interface.

00

H

HMP8190, HMP8191

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HMP8190EVAL1 | NTSC/PAL Video Encoder |

| HMP8191 | NTSC/PAL Video Encoder |

| HMP8191CN | NTSC/PAL Video Encoder |

| HMPS650 | NPN SILICON TRANSISTOR |

| HMPSH10 | NPN EPITAXIAL PLANAR TRANSISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HMP8190EVAL1 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8191 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8191CN | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:NTSC/PAL Video Encoder |

| HMP8201CN | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Compression/Expansion Circuit |

| HMP820SGR32GM | 制造商:Advanced Micro Devices 功能描述:PHENOM II MOBILE X3 P820 25W S1G4 - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。