- 您現在的位置:買賣IC網 > PDF目錄370499 > HDMP-0440 Voltage Regulator IC; Output Current:100mA; Output Voltage:6.2V; Package/Case:3-TO-92; Voltage Regulator Type:Positive Voltage; Mounting Type:Through Hole; Supply Voltage:35V PDF資料下載

參數資料

| 型號: | HDMP-0440 |

| 英文描述: | Voltage Regulator IC; Output Current:100mA; Output Voltage:6.2V; Package/Case:3-TO-92; Voltage Regulator Type:Positive Voltage; Mounting Type:Through Hole; Supply Voltage:35V |

| 中文描述: | 四端口旁路電路的光纖通道仲裁環(huán)路 |

| 文件頁數: | 6/10頁 |

| 文件大?。?/td> | 271K |

| 代理商: | HDMP-0440 |

6

AC Electrical Specifications

T

A

= 0

°

C to +70

°

C, V

CC

= 3.15 V to 3.45 V.

Symbol

Parameter

T

LOOP_LAT

Total Loop Latency from FM_NODE[0] to TO_NODE[0]

T

CELL_LAT

Per Cell Latency from FM_NODE[4] to TO_NODE[0]

t

r,LVTTLin

Input LVTTL Rise Time Requirement, 0.8 V to 2.0 V

t

f,LVTTLin

Input LVTTL Fall Time Requirement, 2.0 V to 0.8 V

t

r,LVTTLout

Output TTL Rise Time, 0.8 V to 2.0 V, 10 pF Load

t

f,LVTTLout

Output TLL Fall Time, 2.0 V to 0.8 V, 10 pF Load

t

rs,HS_OUT

HS_OUT Single-Ended Rise Time, 20% to 80%

t

fs,HS_OUT

HS_OUT Single-Ended Fall Time, 20% to 80%

t

rd,HS_OUT

HS_OUT Differential Rise Time, 20% to 80%

t

fd,HS_OUT

HS_OUT Differential Fall Time, 20% to 80%

V

IP,HS_IN

HS_IN Required Pk-Pk Differential Input Voltage

V

OP,HS_OUT

HS_OUT Pk-Pk Differential Output Voltage (Z0 = 75

, Figure 6)

Units

ns

ns

ns

ns

ns

ns

ps

ps

ps

ps

mV

mV

Min.

Typ.

2.0

0.8

2.0

2.0

1.7

1.7

200

200

200

200

1200

1400

Max.

3.3

2.4

30

300

300

30

2000

2000

200

1100

Guaranteed Operating Rates

T

A

= 0

°

C to +70

°

C, V

CC

= 3.15 V to 3.45 V.

FC Serial Clock Rate (MBd)

Min.

Max.

1,040

1,080

GE Serial Clock Rate (MBd)

Min.

1,240

Max.

1,260

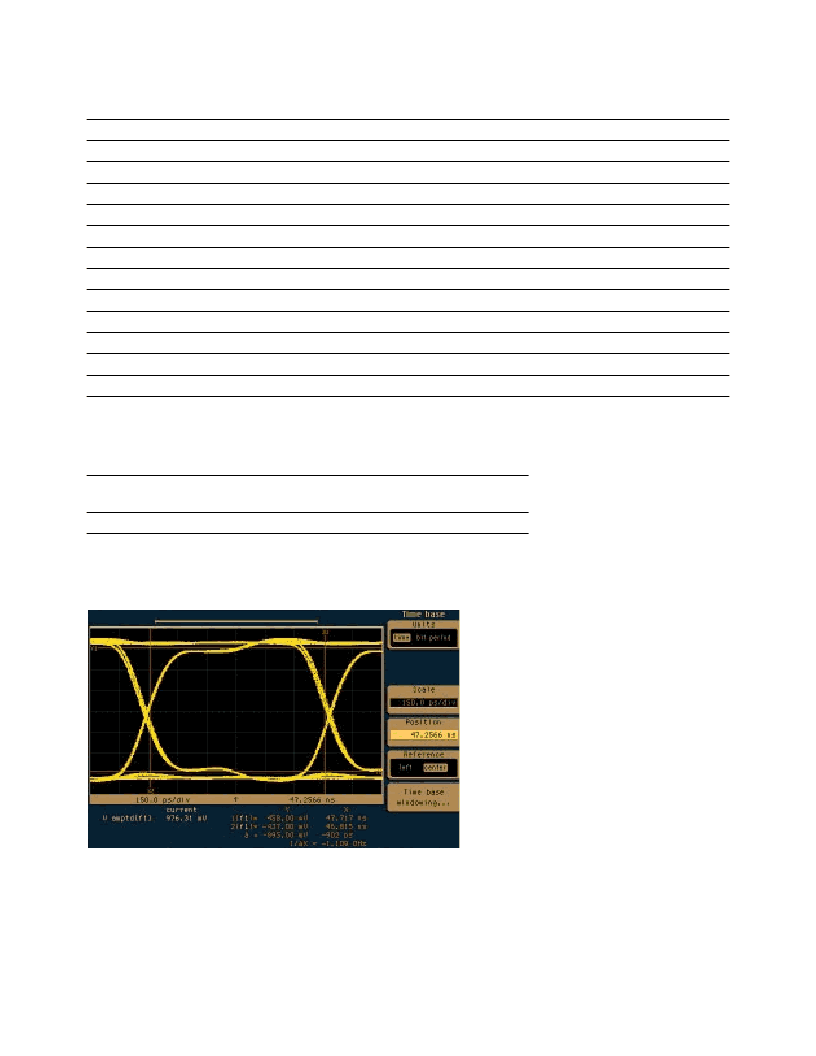

Figue 4. Eye diagram of TO_NODE[1]

±

high speed differential output (50

termination).

Note: Measurement taken with a 2

7

-1 PRBS input to FM_NODE[1]

±

.

相關PDF資料 |

PDF描述 |

|---|---|

| HDMP-0482 | Octal Cell Port Bypass Circuit with CDR and Data Valid Detection |

| HDMP-1012 | Phase Lock Loop (PLL) IC; Number of Circuits:1; Package/Case:14-DIP; Mounting Type:Through Hole |

| HDMP-1014 | Bipolar Transistor; Collector Emitter Voltage, Vceo:400V; Transistor Polarity:N Channel; Power Dissipation:250W; C-E Breakdown Voltage:400V; DC Current Gain Min (hfe):10; Collector Current:50A; Package/Case:TO-3 |

| HDMP-1022 | Audio Power Amplifier; Speaker Channels:Mono; Headphone Channels:Mono; Output Power, Po:2W; Load Impedance Min:8ohm; Supply Voltage Max:24V; Supply Voltage Min:6V |

| HDMP-1024 | Low Cost Gigabit Rate Receive Chip Set with TTL I/Os(帶TTL輸入/輸出的低價格千兆位速率接收芯片) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| HDMP-0450 | 制造商:Agilent Technologies 功能描述: |

| HDMP-0451 | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述: |

| HDMP-0451G | 制造商:Rochester Electronics LLC 功能描述: 制造商:PMC-Sierra 功能描述: |

| HDMP-0452 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Quad Port Bypass Circuit with CDR for Fibre Channel Arbitrated Loops |

| HDMP-0480 | 制造商:AGILENT 制造商全稱:AGILENT 功能描述:Octal Cell Port Bypass Circuit without Clock and Data Recovery |

發(fā)布緊急采購,3分鐘左右您將得到回復。