- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383012 > GMS87C7216Q (Electronic Theatre Controls, Inc.) 8-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號(hào): | GMS87C7216Q |

| 廠商: | Electronic Theatre Controls, Inc. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | 8位單晶片微控制器 |

| 文件頁(yè)數(shù): | 81/121頁(yè) |

| 文件大小: | 1645K |

| 代理商: | GMS87C7216Q |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)當(dāng)前第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)

GMS81C7208/7216

FEB. 2005 Ver 1.04

77

20.2 STOP Mode

For applications where power consumption is a critical

factor, device provides reduced power of STOP.

Start the Stop Operation

An instruction that STOP causes to be the last instruction

is executed before going into the STOP mode. In the Stop

mode, the on-chip main-frequency oscillator is stopped.

With the clock frozen, all functions are stopped, but the on-

chip RAM and Control registers are held. The port pins

output the values held by their respective port data register,

the port direction registers. The status of peripherals during

Stop mode is shown below.

Note:

Since the X

IN

pin is connected internally to GND to

avoid current leakage due to the crystal oscillator in STOP

mode, do not use STOP instruction when an external clock

is used as the main system clock.

In the Stop mode of operation, V

DD

can be reduced to minimize

power consumption. Be careful, however, that V

DD

is not re-

duced before the Stop mode is invoked, and that V

DD

is restored

to its normal operating level before the Stop mode is terminated.

The reset should not be activated before V

DD

is restored to its

normal operating level, and must be held active long enough to

allow the oscillator to restart and stabilize.

And after STOP instruction, at least two or more NOP instruction

should be written as shown in example below.

Example)

LDM

LDM

STOP

NOP

NOP

CKCTLR,#0EBH;32.8ms

CKCTLR,#0FBH ;65.5ms

;

:

The interval timer register CKCTLR should be initialized (0F

H

or

0E

H

) by software in order that oscillation stabilization time

should be longer than 20ms before STOP mode.

Release the STOP Mode

The exit from STOP mode is using hardware reset or external in-

terrupt, watch timer, key scan or Timer/Counter.

To release STOP mode, corresponding interrupt should be

enabled before STOP mode.

Specially as a clock source of Timer/Event Counter, EC0 or EC2

pin can release it by Timer/Event Counter

interrupt request

.

Reset redefines all the control registers but does not change the

on-chip RAM. External interrupts allow both on-chip RAM and

Control registers to retain their values.

Start-up is performed to acquire the time for stabilizing oscilla-

tion. During the start-up, the internal operations are all stopped.

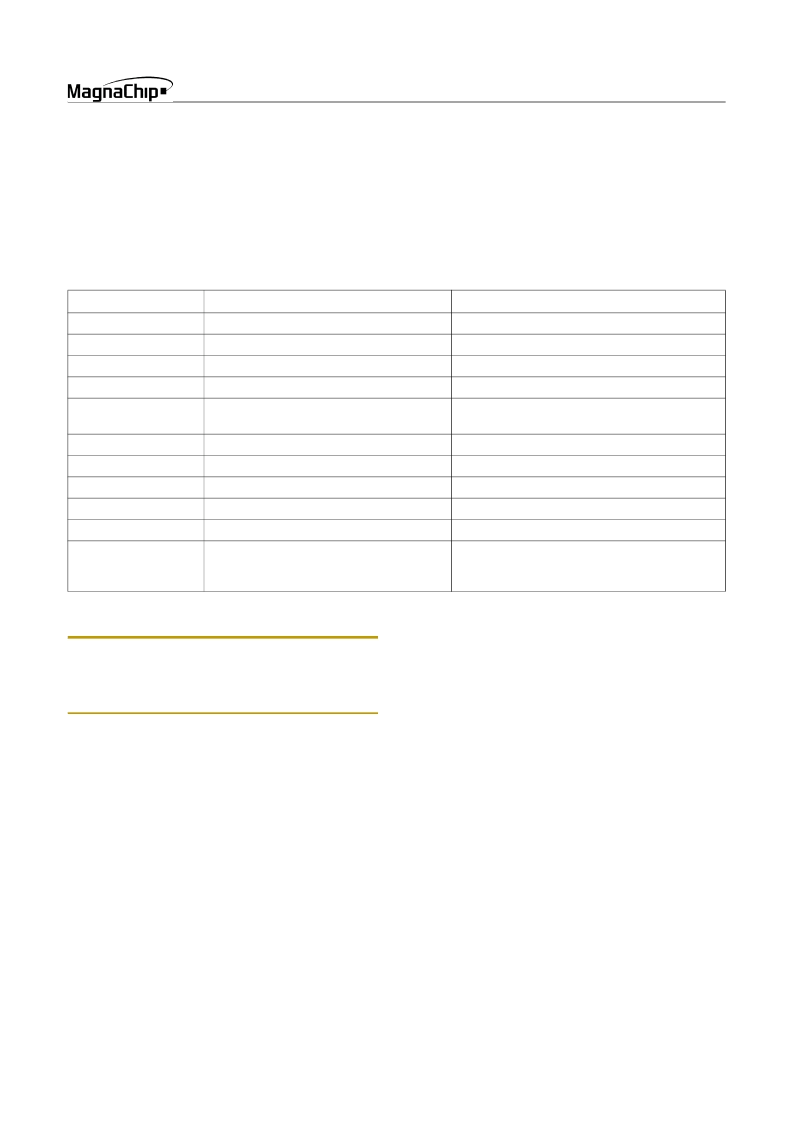

Peripheral

STOP Mode

SLEEP Mode

CPU

All CPU operations are disabled

All CPU operations are disabled

RAM

Retain

Retain

LCD Driver

LCD driver operates continuously

LCD driver operates continuously

Basic Interval Timer

Halted

BIT operates continuously

Timer/Event Counter

Halted (Only when the Event counter mode

is enabled, Timer operates normally)

Timer/Event Counter operates continuously

Watch Timer

Watch Timer operates continuously

Watch Timer operates continuously

Main-oscillation

Stop (X

IN

pin = “L”, X

OUT

pin = ”L”)

Oscillation

Oscillation

Sub-oscillation

Oscillation

I/O Ports

Retain

Retain

Control Registers

Retain

Retain

Release Method

RESET, SIO interrupt, Watch Timer inter-

rupt, Timer interrupt (EC0,2), External inter-

rupt

RESET, All interrupts

Table 20-1 Peripheral Operation During Power Down Mode

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GMS87C7216LQ | 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GNR20D101K | VARISTOR |

| GNR20D102K | VARISTOR |

| GNR20D112K | VARISTOR |

| GNR20D121K | VARISTOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| GM-S-88 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLACK RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點(diǎn)數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點(diǎn)電鍍: 外殼材料:Thermoplastic IP 等級(jí): |

| GM-S-88-50 | 功能描述:以太網(wǎng)和電信連接器 8P8C R/A PCB SHIELD LOW PROFILE BLK 50u RoHS:否 制造商:Pulse 產(chǎn)品:Modular Jacks 性能類別: USOC 代碼:RJ45 位置/觸點(diǎn)數(shù)量: 安裝風(fēng)格:Through Hole 端口數(shù)量:1 x 1 型式:Female 屏蔽: 電流額定值: 電壓額定值: 觸點(diǎn)電鍍: 外殼材料:Thermoplastic IP 等級(jí): |

| GMS90 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS90C31 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

| GMS90C32 | 制造商:HYNIX 制造商全稱:Hynix Semiconductor 功能描述:HYNIX SEMICONDUCTOR INC. 8-BIT SINGLE-CHIP MICROCONTROLLERS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。