- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4344 > EP4SGX70HF35I4N (Altera)IC STRATIX IV FPGA 70K 1152FBGA PDF資料下載

參數(shù)資料

| 型號: | EP4SGX70HF35I4N |

| 廠商: | Altera |

| 文件頁數(shù): | 52/82頁 |

| 文件大小: | 0K |

| 描述: | IC STRATIX IV FPGA 70K 1152FBGA |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 3 |

| 系列: | Stratix® IV GX |

| LAB/CLB數(shù): | 2904 |

| 邏輯元件/單元數(shù): | 72600 |

| RAM 位總計: | 7564880 |

| 輸入/輸出數(shù): | 488 |

| 電源電壓: | 0.87 V ~ 0.93 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 1152-BBGA |

| 供應(yīng)商設(shè)備封裝: | 1152-FBGA(27x27) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁當(dāng)前第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁

1–48

Chapter 1: DC and Switching Characteristics for Stratix IV Devices

Switching Characteristics

Stratix IV Device Handbook

March 2014

Altera Corporation

Volume 4: Device Datasheet and Addendum

PLL Specifications

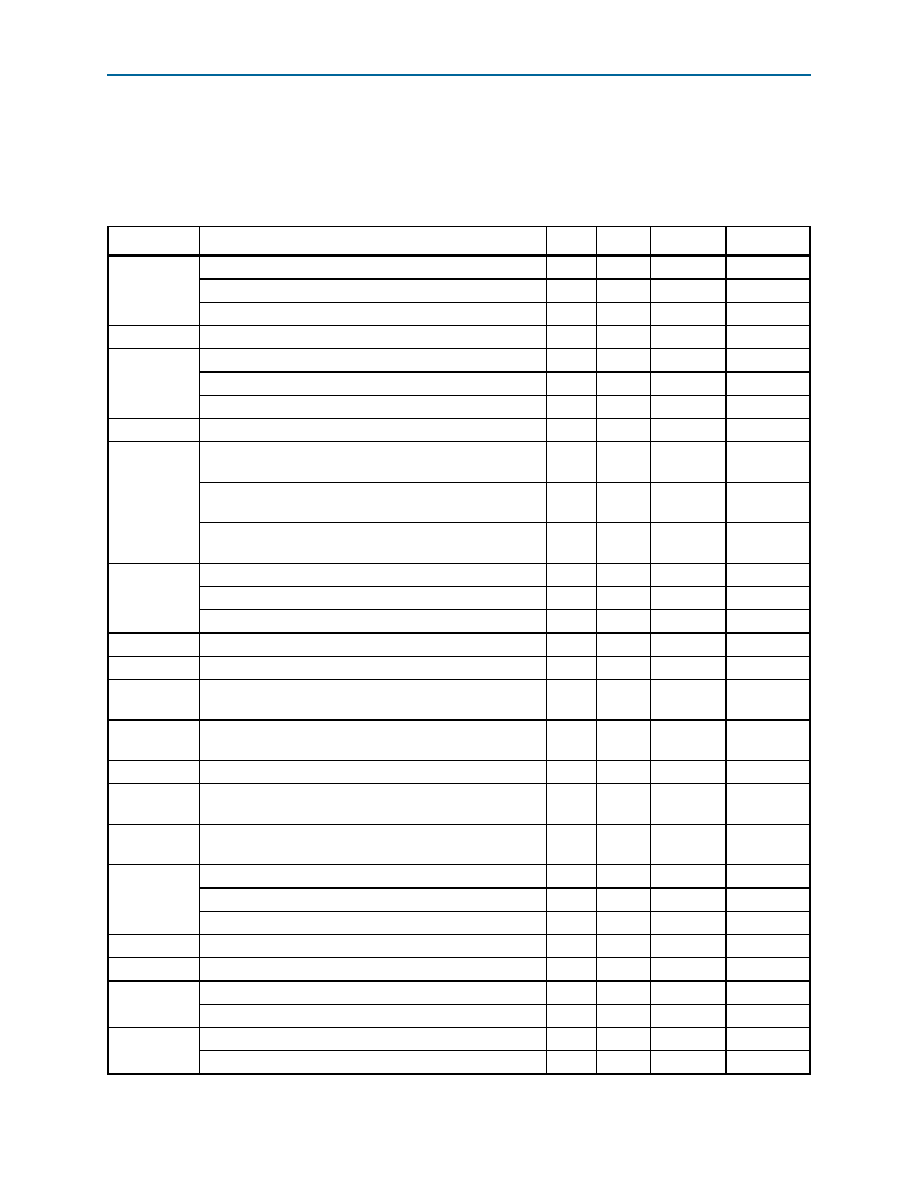

Table 1–34 lists the Stratix IV PLL specifications when operating in the commercial

(0° to 85°C), industrial (–40° to 100°C), and military (–55°C to 125°C) junction

temperature ranges.

Table 1–34. PLL Specifications for Stratix IV Devices (Part 1 of 2)

Symbol

Parameter

Min

Typ

Max

Unit

fIN

Input clock frequency (–2/–2x speed grade)

5

—

800 (1)

MHz

Input clock frequency (–3 speed grade)

5

—

717 (1)

MHz

Input clock frequency (–4 speed grade)

5

—

717 (1)

MHz

fINPFD

Input frequency to the PFD

5

—

325

MHz

fVCO (2)

PLL VCO operating range (–2 speed grade)

600

—

1600

MHz

PLL VCO operating range (–3 speed grade)

600

—

1300

MHz

PLL VCO operating range (–4 speed grade)

600

—

1300

MHz

tEINDUTY

Input clock or external feedback clock input duty cycle

40

—

60

%

fOUT

Output frequency for internal global or regional clock

(–2/–2x speed grade)

—

800 (3)

MHz

Output frequency for internal global or regional clock

(–3 speed grade)

—

717 (3)

MHz

Output frequency for internal global or regional clock

(–4 speed grade)

—

717 (3)

MHz

fOUT_EXT

Output frequency for external clock output (–2 speed grade)

—

800 (3)

MHz

Output frequency for external clock output (–3 speed grade)

—

717 (3)

MHz

Output frequency for external clock output (–4 speed grade)

—

717 (3)

MHz

tOUTDUTY

Duty cycle for external clock output (when set to 50%)

45

50

55

%

tFCOMP

External feedback clock compensation time

—

10

ns

tCONFIGPLL

Time required to reconfigure scan chain

—

3.5

—

scanclk

cycles

tCONFIGPHASE

Time required to reconfigure phase shift

—

1

—

scanclk

cycles

fSCANCLK

scanclk frequency

—

100

MHz

tLOCK

Time required to lock from end-of-device configuration or

de-assertion of areset

——

1

ms

tDLOCK

Time required to lock dynamically (after switchover or

reconfiguring any non-post-scale counters/delays)

——

1

ms

fCLBW

PLL closed-loop low bandwidth

—

0.3

—

MHz

PLL closed-loop medium bandwidth

—

1.5

—

MHz

PLL closed-loop high bandwidth (8)

—4

—

MHz

tPLL_PSERR

Accuracy of PLL phase shift

—

±50

ps

tARESET

Minimum pulse width on the areset signal

10

—

ns

Input clock cycle to cycle jitter (FREF ≥ 100 MHz)

—

0.15

UI (p-p)

Input clock cycle to cycle jitter (FREF < 100 MHz)

—

±750

ps (p-p)

tOUTPJ_DC (6)

Period Jitter for dedicated clock output (FOUT ≥ 100 MHz)

—

175

ps (p-p)

Period Jitter for dedicated clock output (FOUT < 100 MHz)

—

17.5

mUI (p-p)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| EP2AGX125DF25I5 | IC ARRIA II GX FPGA 125K 572FBGA |

| 24LC01B/ST | IC EEPROM 1KBIT 400KHZ 8TSSOP |

| EP2AGX125DF25C4 | IC ARRIA II GX FPGA 125K 572FBGA |

| EP1SGX25FF1020C6 | IC STRATIX GX FPGA 25K 1020-FBGA |

| ABB92DHFD-S329 | EDGECARD PCI 184PS .050 SMD 3.3V |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EP4-SI | 制造商:Box Enclosures & Assembly Services 功能描述:END PLATE FOR SERIES 4, SILVER ANODIZED, 2.11 H X 6.68 W 制造商:Box Enclosures & Assembly Services 功能描述:Enclosure End Plate 制造商:Box Enclosures & Assembly Services 功能描述:END PLATE; Accessory Type:End Plate; For Use With:Extruded Aluminum Enclosures, BEX Series 4; Body Color:Silver; Body Material:Aluminum; External Height:2.11"; External Width:6.68"; Features:Silver; Leaded Process Compatible:Yes ;RoHS Compliant: Yes |

| EP4-SPR-BULK | 功能描述:SONIC DEFENDER SMALL CLEAR RoHS:是 類別:音頻產(chǎn)品 >> 配件 系列:EarPro 標(biāo)準(zhǔn)包裝:1 系列:- 附件類型:墊圈 材質(zhì):氯丁橡膠 顏色:黑 適用于相關(guān)產(chǎn)品:Sonalert? 信號設(shè)備 其它名稱:458-1048 |

| EP5 | 制造商:Datak Corporation 功能描述: |

| EP-5 | 制造商:Mac8 功能描述: 制造商:Curtis Industries 功能描述: |

| EP501 | 制造商:ACTEL 制造商全稱:Actel Corporation 功能描述:EP501 NAND Flash Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。