- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄97869 > DS3112N (DALLAS SEMICONDUCTOR) DATACOM, FRAMER, PBGA256 PDF資料下載

參數(shù)資料

| 型號(hào): | DS3112N |

| 廠商: | DALLAS SEMICONDUCTOR |

| 元件分類: | Digital Transmission Controller |

| 英文描述: | DATACOM, FRAMER, PBGA256 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-256 |

| 文件頁(yè)數(shù): | 63/134頁(yè) |

| 文件大小: | 900K |

| 代理商: | DS3112N |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)當(dāng)前第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)

DS3112

34 of 134

Bit 7 / T3/E3 Transmit Frame Sync I/O Control (FTSOFC). When this bit is set low, the FTSOF

signal will be an output and will pulse for one FTCLK cycle at the beginning of each frame. When this

bit is high, the FTSOF signal is an input and the device uses it to determine the frame boundaries.

0 = FTSOF is an output

1 = FTSOF is an input

Bit 8 / Low Speed (T1/E1) Transmit Port Common Clock Enable (LTCCEN). When this bit is set

high, the LTCLK1 to LTCLK28 and LTCLKA and LTCLKB inputs are ignored and a common clock

sourced via the LTCCLK input is used in their place.

0 = disable LTCCLK

1 = enable LTCCLK

Bit 9 / Low Speed (T1/E1) Receive Port Common Clock Enable (LRCCEN). When this bit is set

high, the LRCLK1 to LRCLK28 and LRCLKA and LRCLKB outputs will all be sourced from the

LRCCLK input. This configuration can only be used in applications where it can be insured that all of

the T1 or E1 channels from the far end are being sourced from a common clock.

0 = disable LRCCLK

1 = enable LRCCLK

Bit 10 / High Speed (T3/E3) Data Enable Mode Select (DENMS). When this bit is set low, the

FRDEN and FTDEN outputs will be asserted during payload data and deasserted during overhead data.

When this bit is high, FRDEN and FTDEN are gapped clocks that pulse during payload data and are

suppressed during overhead data.

0 = FRDEN and FTDEN are Data Enables

1 = FRDEN and FTDEN are Gapped Clocks

Bit 11 / Low Speed (T1/E1) Port Loop Timed Mode (LLTM). When this bit is set low, the low speed

T1 and E1 receive clocks (LRCLK) are not routed to the transmit side. When this bit is high, the

LRCLKs are routed to the transmit side to be used as the transmit T1 and E1 clocks. When enabled, all

the low speed ports are looped timed. This control bit affects all the low speed ports. The device is not

capable of setting individual low speed ports into and out of looped timed mode. See the Block Diagram

in Figures 1A and 1B for more details.

0 = disable loop timed mode (LRCLK is not used to replace the associated LTCLK)

1 = enable loop timed mode (LRCLK replaces the associated LTCLK)

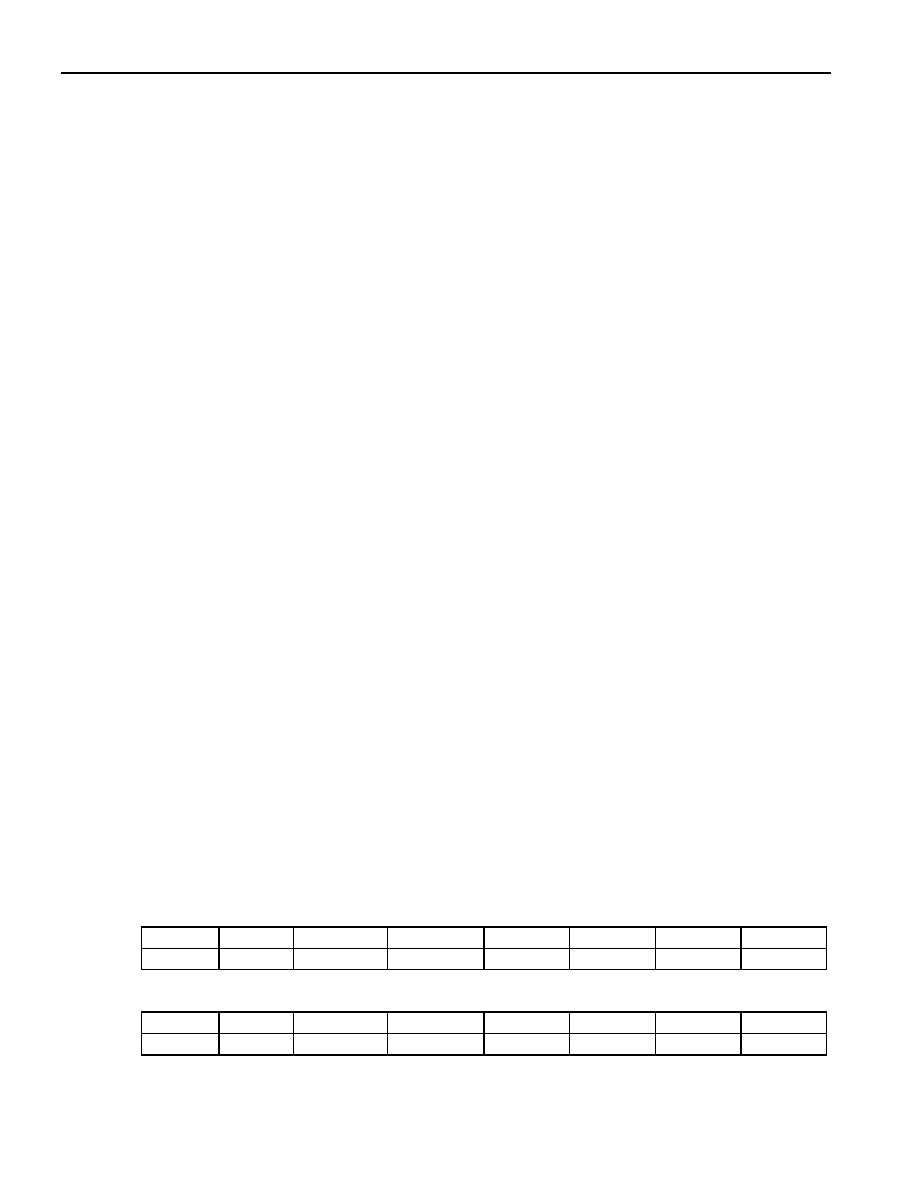

Register Name:

MC2

Register Description:

Master Configuration Register 2

Register Address:

04h

Bit #

7

6

5

4

3210

Name

n/a

HTDATL

HTDATH

HRDATI HRCLKI HTDATI HTCLKI

Default

-

0

0000

Bit #

15

14

13

12

11

10

9

8

Name

n/a

LRDATI

LRCLKI

LTDATI

LTCLKI

Default

-

0000

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DS3112 | DATACOM, FRAMER, PBGA256 |

| DS3131 | SPECIALTY TELECOM CIRCUIT, PBGA256 |

| DS3134 | DATACOM, FRAMER, PBGA256 |

| DS3150QN | DATACOM, PCM TRANSCEIVER, PQCC28 |

| DS3150Q | DATACOM, PCM TRANSCEIVER, PQCC28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DS3112N+ | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112N+W | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC TEMPE T3/E3 MUX FRMR & M13/E13/G.747 MUX RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

| DS3112NC1 | 制造商:Maxim Integrated Products 功能描述:T3 E3 MULTIPLEXER, 3.3V T3/E3 FRAMER AND M13/E13/G.747 MUX - Rail/Tube |

| DS3112ND1E | 制造商:Rochester Electronics LLC 功能描述: 制造商:Maxim Integrated Products 功能描述: |

| DS3112RD | 功能描述:網(wǎng)絡(luò)控制器與處理器 IC RoHS:否 制造商:Micrel 產(chǎn)品:Controller Area Network (CAN) 收發(fā)器數(shù)量: 數(shù)據(jù)速率: 電源電流(最大值):595 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:PBGA-400 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。