- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375269 > ADV7195 (Analog Devices, Inc.) Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input PDF資料下載

參數(shù)資料

| 型號: | ADV7195 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| 中文描述: | 多格式逐行掃描/高清晰度電視編碼器三種11位DAC和10位數(shù)據(jù)輸入 |

| 文件頁數(shù): | 26/36頁 |

| 文件大小: | 499K |

| 代理商: | ADV7195 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

REV. 0

ADV7195

–26–

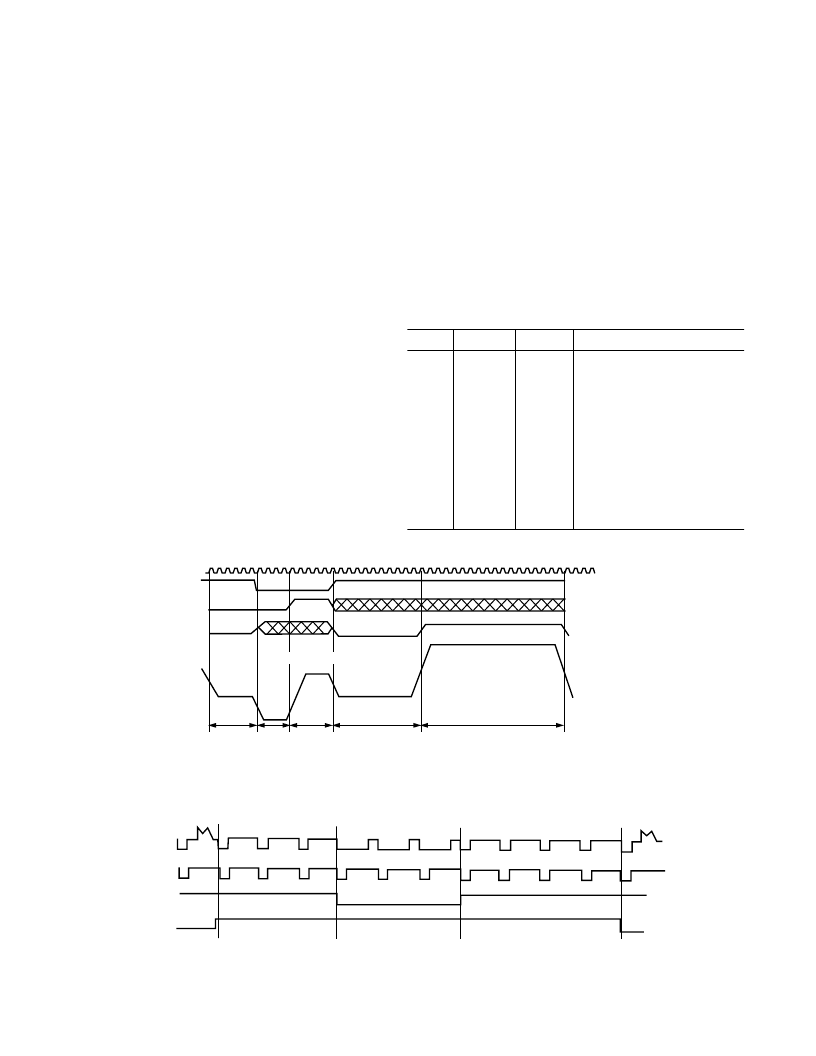

Figure 49 shows an example of how to program the ADV7195

to accept a different high definition standard but SMPTE293M,

SMPTE274M, SMPTE296M or ITU-R.BT1358 standard.

Reserved (MR04)

A “0” must be written to this bit.

Input Standard (MR05)

Select between 1080i or 720p input.

DV Polarity (MR06)

This control bit allows to select the polarity of the DV input

control signal to be either active high or active low.

Reserved (MR07)

A “0” must be written to this bit.

Table IX. Truth Table

SYNC

TSYNC

DV

1 –> 0

0

0 or 1

50% Point of Falling Edge of

Tri-Level Horizontal Sync

Signal, A

25% Point of Rising Edge of

Tri-Level Horizontal Sync

Signal, B

50% Point of Falling Edge of

Tri-Level Horizontal Sync

Signal, C

50% Start of Active Video, D

50% End of Active Video, E

0

0 –> 1

0 or 1

0 –> 1

0 or 1

0

1

1

0 or 1

0 or 1

0 –> 1

1 –> 0

CLK

SYNC

TSYNC

DV

SET MR06 = 1

PROGRAMMABLE

INPUT TIMING

ANALOG

OUTPUT

A

B

C

D

E

243

ACTIVE VIDEO

1920

66

66

81

HORIZONTAL SYNC

Figure 48. Async Timing Mode—Programming Input Control Signals for SMPTE295M Compatibility

VIDEO

OUTPUT

HSYNC

525

VSYNC

DV

1

12

13

42

43

Figure 49. DV Input Control Signal in Relation to Video Output Signal

HDTV MODE

MODE REGISTER 0

MR0 (MR07–MR00)

(Address (SR4–SR0) = 00H)

Figure 50 shows the various operations under the control of

Mode Register 0.

MR0 BIT DESCRIPTION

Output Standard Selection (MR00-MR01)

These bits are used to select the output levels from the ADV7195.

If EIA-770.3 (MR01–00 = “00”) is selected, the output levels will

be: 0 mV for blanking level, 700 mV for peak white (Y channel),

±

350 mV for Pr, Pb outputs and –300 mV for tri-level sync.

If Full Input Range (MR01–00 = “10”) is selected, the output

levels will be 700 mV for peak white for the Y channel,

±

350 mV

for Pr, Pb outputs and –300 mV for Sync. This mode is used for

RS-170, RS-343A standard output compatibility.

Sync insertion on the Pr, Pb channels is optional. For output

levels, refer to the Appendix.

Input Control Signals (MR02–MR03)

These control bits are used to select whether data is input with

external horizontal, vertical and blanking sync signals or if the

data is input with embedded EAV/SAV codes. An Asynchro-

nous timing mode is also available using TSYNC,

SYNC

and

DV as input control signals. These timing control signals have

to be programmed by the user.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7195KST | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| ADV7196 | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196A | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196AKS | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7197 | Multiformat HDTV Encoder with Three 11-Bit DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7195KS | 制造商:Analog Devices 功能描述:Video Encoder 3DAC 11-Bit 52-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:MULTI-FORMAT VID+PROGSCAN/HDTV ENCODERIC - Bulk |

| ADV7195KST | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| ADV7195KSZ | 制造商:Analog Devices 功能描述:Video Encoder 3DAC 11-Bit 52-Pin MQFP |

| ADV7196 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

發(fā)布緊急采購,3分鐘左右您將得到回復。