- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375269 > ADV7195 (Analog Devices, Inc.) Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input PDF資料下載

參數(shù)資料

| 型號(hào): | ADV7195 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| 中文描述: | 多格式逐行掃描/高清晰度電視編碼器三種11位DAC和10位數(shù)據(jù)輸入 |

| 文件頁(yè)數(shù): | 18/36頁(yè) |

| 文件大小: | 499K |

| 代理商: | ADV7195 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)當(dāng)前第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

REV. 0

ADV7195

–18–

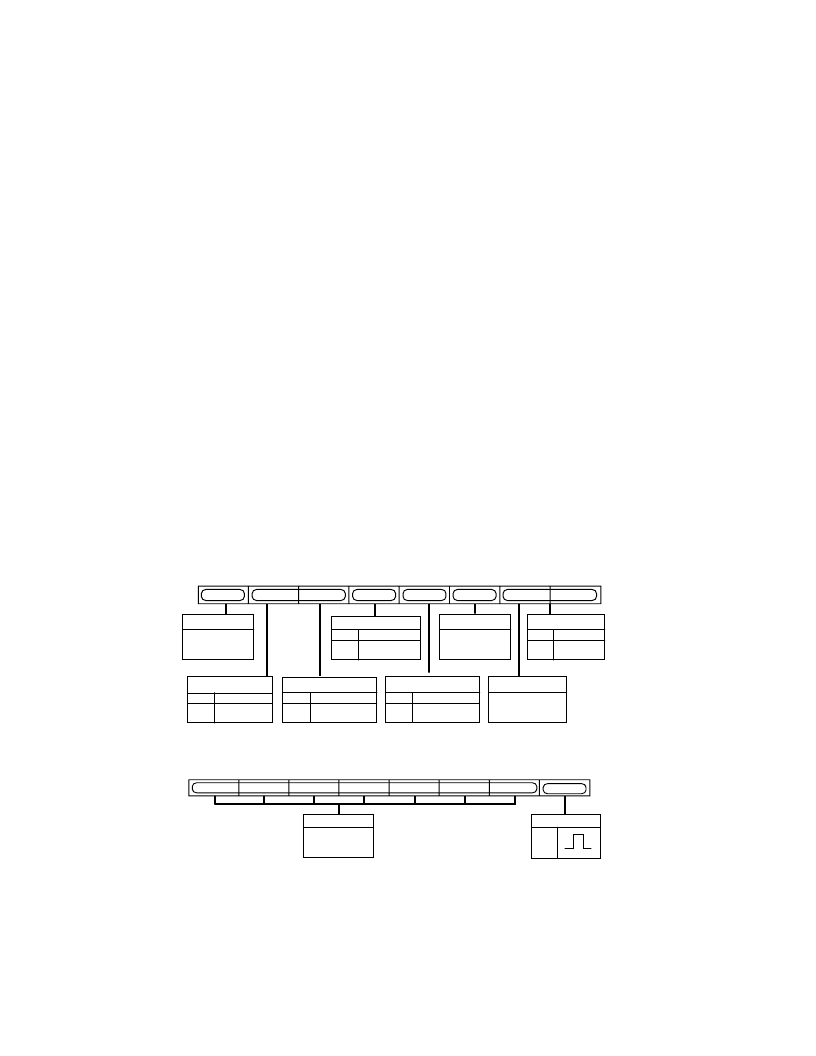

MODE REGISTER 4

MR4 (MR47–MR40)

(Address (SR4–SR0) = 04H)

Figure 24 shows the various operations under the control of

Mode Register 4.

MR4 BIT DESCRIPTION

Timing Reset (MR40)

Toggling MR40 from low to high and low again resets the inter-

nal horizontal and vertical timing counters.

MODE REGISTER 5

MR5 (MR57–MR50)

(Address (SR4-SR0) = 05H)

Figure 25 shows the various operations under the control of

Mode Register 5.

MR5 BIT DESCRIPTION

Reserved (MR50)

This bit is reserved for the revision code.

RGB Mode (MR51)

When RGB mode is enabled (MR51 = “1”) the ADV7195

accepts unsigned binary RGB data at its input port. This control

is also available in Async Timing Mode.

Sync on PrPb (MR52)

By default, the color component output signals Pr, Pb do not

contain any horizontal sync pulses. They can be inserted when

MR52 = “1.” This facility is only available when Output Stan-

dard Selection has been set to EIA-770.2 (MR01–00 = “00”) or

Full Input Range (MR01–00 = “10”).

This control is not available in RGB mode.

MODE REGISTER 3

MR3 (MR37–MR30)

(Address (SR4–SR0) = 03H)

Figure 23 shows the various operations under the control of

Mode Register 3.

MR3 BIT DESCRIPTION

HDTV Enable (MR30)

When this bit is set to “1,” the ADV7195 reverts to HDTV mode

(refer to HDTV mode section). When set to “0” the ADV7195

is set up in Progressive Scan Mode (PS Mode).

Reserved (MR31–MR32)

A “0” must be written to these bits.

DAC A Control (MR33)

Setting this bit to “1” enables DAC A, otherwise this DAC is

powered down.

DAC B Control (MR34)

Setting this bit to “1” enables DAC B, otherwise this DAC is

powered down.

DAC C Control (MR35)

Setting this bit to “1” enables DAC C, otherwise this DAC is

powered down.

Interpolation (MR36)

This bit enables the second stage interpolation filters. When this

bit is enabled (MR36 = “1”), data is sent at 54 MHz to the DAC

output stage. After Reset it is recommended to toggle this bit.

Before toggling this bit, 3Ehex must be written to address 09hex

to guarantee correct operation.

Reserved (MR37)

A “0” must be written to this bit.

ZWRITTEN TO

THIS BIT

MR37

MR36

MR35

MR34

MR33

MR32

MR31

MR30

HDTV ENABLE

0

1

DISABLE

MR30

0

1

POWER-DOWN

MR34

DAC A CONTROL

MR33

0

1

POWER-DOWN

NORMAL

DAC B CONTROL

ZERO MUST BE

WTHIS BIT

INTERPOLATION

MR36

0

1

DISABLE

ENABLE

DAC C CONTROL

MR35

0

1

POWER-DOWN

NORMAL

MR31

ZWRITTEN TO

THIS BIT

MR37

MR32

Figure 23. Mode Register 3

MR47

MR46

MR45

MR44

MR43

MR42

MR41

MR40

MR47

–

MR41

MR40

TIMING RESET

ZWRITTEN TO

THESE BITS

Figure 24. Mode Register 4

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ADV7195KST | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| ADV7196 | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196A | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196AKS | Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7197 | Multiformat HDTV Encoder with Three 11-Bit DACs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ADV7195KS | 制造商:Analog Devices 功能描述:Video Encoder 3DAC 11-Bit 52-Pin MQFP 制造商:Rochester Electronics LLC 功能描述:MULTI-FORMAT VID+PROGSCAN/HDTV ENCODERIC - Bulk |

| ADV7195KST | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs and 10-Bit Data Input |

| ADV7195KSZ | 制造商:Analog Devices 功能描述:Video Encoder 3DAC 11-Bit 52-Pin MQFP |

| ADV7196 | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

| ADV7196A | 制造商:AD 制造商全稱:Analog Devices 功能描述:Multiformat Progressive Scan/HDTV Encoder with Three 11-Bit DACs, 10-Bit Data Input, and Macrovision |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。