- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄165343 > AD7467BRT (ANALOG DEVICES INC) 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 PDF資料下載

參數(shù)資料

| 型號: | AD7467BRT |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 |

| 中文描述: | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO6 |

| 封裝: | MO-178AB, SOT-23, 6 PIN |

| 文件頁數(shù): | 22/24頁 |

| 文件大小: | 327K |

| 代理商: | AD7467BRT |

–7–

REV. PrF

PRELIMINARY TECHNICAL DATA

AD7466/AD7467/AD7468

Timing Example 1

From Figure 3, having

fSCLK = 3.4MHz and a throughput of 100 KSPS, gives a cycle time of tCONVERT+ t8 + tQUIET =

10

s. With t

CONVERT = t2 + 15(1/fSCLK) = 10 ns + 4.41s = 4.42 s, and t8 = TBD ns min, this leaves tQUIET to be TBD

ns. This TBD ns satisfies the requirement of TBD ns for tQUIET. The part is fully powered up and the signal is fully

acquired at point A, that means the acquisition/power up time is t2 + 2(1/fSCLK) = 10 ns + 0.588 s = 0.59 s satisfying

the maximum requirement of TBD s for the power up time.

Timing Example 2

The AD7466 can also operate with slower clock frequencies. From Figure 3, having

fSCLK = 2MHz and a throughput of

50 KSPS, gives a cycle time of

tCONVERT+ t8 + tQUIET = 20

s. With t

CONVERT = t2 + 15(1/fSCLK) = 10 ns + 7.5s = 7.51

s, and t8 = TBD ns min, this leaves tQUIET to be TBD ns. This TBD ns satisfies the requirement of TBD ns for tQUIET.

The part is fully powered up and the signal is fully acquired at point A, that means the acquisition/power up time is t2 +

2(1/fSCLK) = 10 ns + 1 s = 1.01 s, satisfying the maximum requirement of TBD s for the power up time. As in this

example and with other slower clock values, the part will be fully powered up and the signal already be acquired before

the third SCLK falling edge, however the Track and Hold will not go into hold mode until that point. In this example,

the part may be powered up and the signal may

be fully acquired at approximately point B in Figure 3.

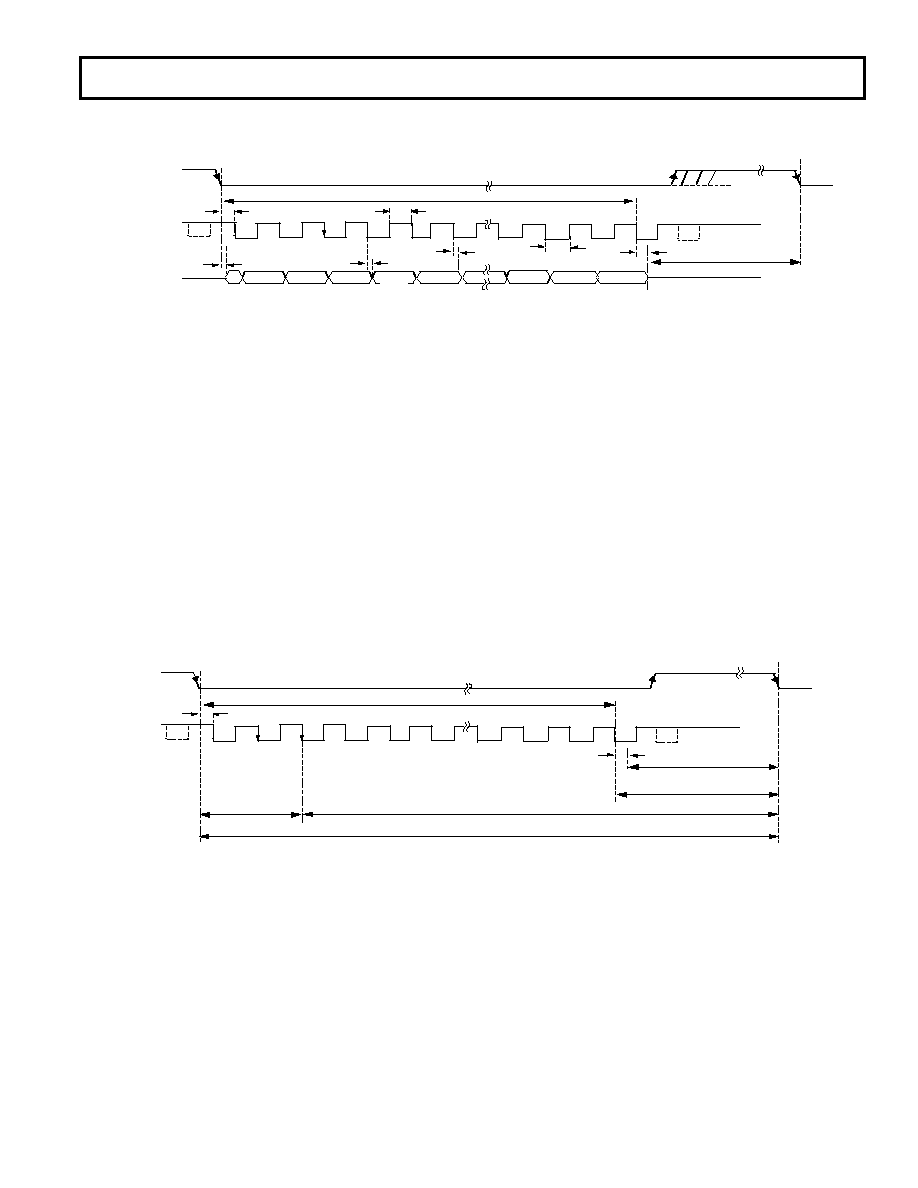

Figure 2. AD7466 Serial InterfaceTiming Diagram

Figures 2 and 3 show some of the timing parameters from the Timing Specifications Section.

&6

SCLK

1

5

13

15

SDATA

4 LEADING ZERO’S

3-STATE

t 4

2

34

16

t5

t3

tQUIET

tCONVERT

t2

3-STATE

DB11

DB10

DB2

DB0

t6

t7

t8

14

ZE RO

ZERO

Z

A

DB1

Figure 3. Serial InterfaceTiming Example

SCLK

1

5

2

34

&6

13

15

16

tQUIET

t2

t 8

14

A

1/THROUGHPUT

tCONVERT

Track/Hold in Track

Automatic Power down

Track/Hold in Hold

PointA: The part is fully poweredupwithVIN fully acquired

B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7468BRT | 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 |

| AD7466 | 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 |

| AD7467 | 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 |

| AD7468 | 1.8 V, Micro-Power, 8/10/12-Bit ADCs in 6 Lead SOT-23 |

| AD746A | Dual Precision, 500 ns Settling, BiFET Op Amp |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7467BRT-R | 制造商:AD 制造商全稱:Analog Devices 功能描述:1.6 V, Micropower 12-/10-/8-Bit ADCs |

| AD7467BRT-R2 | 功能描述:IC ADC 10BIT 1.6V LP SOT23-6 RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 產(chǎn)品培訓(xùn)模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標(biāo)準(zhǔn)包裝:2,500 系列:- 位數(shù):12 采樣率(每秒):3M 數(shù)據(jù)接口:- 轉(zhuǎn)換器數(shù)目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應(yīng)商設(shè)備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數(shù)目和類型:- |

| AD7467BRT-REEL | 制造商:AD 制造商全稱:Analog Devices 功能描述:1.6 V, Micropower 12-/10-/8-Bit ADCs |

| AD7467BRT-REEL7 | 制造商:AD 制造商全稱:Analog Devices 功能描述:1.6 V, Micropower 12-/10-/8-Bit ADCs |

| AD7467BRTZ-R | 制造商:AD 制造商全稱:Analog Devices 功能描述:1.6 V, Micropower 12-/10-/8-Bit ADCs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。