- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36339 > 935264533557 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號: | 935264533557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | SOT-317, MQFP-100 |

| 文件頁數(shù): | 19/43頁 |

| 文件大小: | 254K |

| 代理商: | 935264533557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

1999 March 01

26

Philips Semiconductors

Product specication

Single chip DVB-C channel receiver

VES1820X

DESCI

DESCrambler

Inhibition

parameter.

When

set

high,

DESCI

inhibits

the

descrambling process within the VES1820X. The default value is DESCI = 0

which means "descrambler validated ".

RSI

Reed Solomon Inhibition parameter. When set high, RSI inhibits the correction

procedure of the RS decoder within the VES1820X. The MSB of the second byte

(error indicator) is not set high even if the provided packet is uncorrectable. The

default value is RSI = 0 which means "correction capability of RS decoder

validated ".

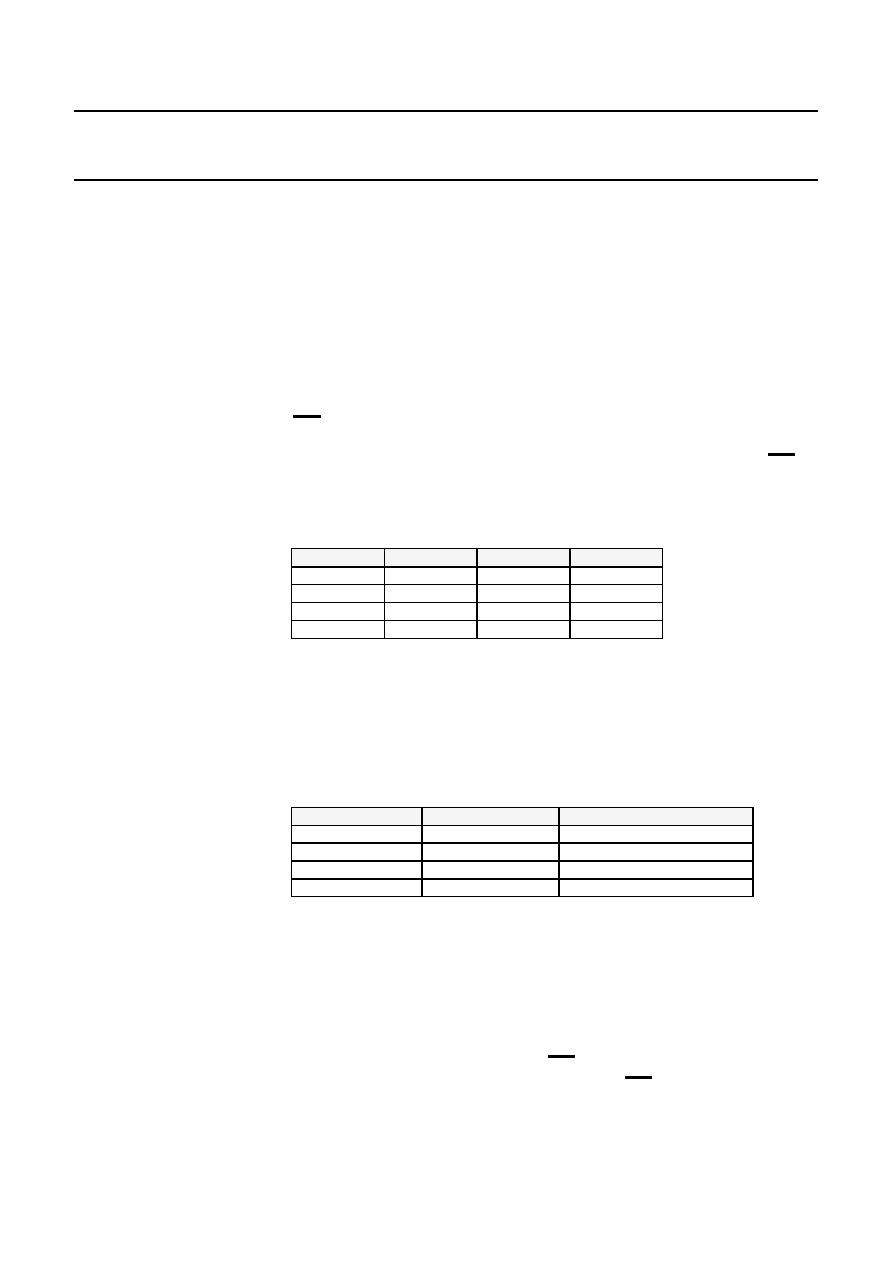

C[1:0]

C[1:0] sets the two parameters (

α,β) used in the synchronization block. In the

frame acquisition phase,

α defines the number of consecutive MPEG2 sync (or

sync ) that the VES1820X must find to declare the deinterleaver synchronized and

to switch to the tracking phase.

In the tracking phase,

β defines the number of consecutive MPEG2 sync (or sync )

that the VES1820X must miss to declare the deinterleaver desynchronized and to

switch back to the sync phase.The default value is C[1:0] = 3

16

which

corresponds to

α = 6 and β = 15.

C[1]

C[0]

α

β

0056

0158

106

10

116

15

CLB_UNC

CLBUNC is an active low reset signal which clears the 7-bit counter used to

memorize

the

number

of

uncorrectable

packets

contained

in

register

CPT_UNCOR. To clear the counter first write CLB_UNC=0 then CLB_UNC=1

(default).

PVBER[1/0]

These two bits allow to program the number of bits of the sequence length where

the demodulator output Bit Error Rate is computed. The number of bits varies from

10

5 to 108 bits. The default value is PVBER = 1

16 which corresponds to 10

6 bits.

PVBER[1]

PVBER[0]

Number of bits

00

10

5

01

10

6

10

7

11

10

8

18. SYNC

11

16

READ ONLY

EQ_ALGO

EQ_ALGO indicates whether the current algorithm used for equalization is the

acquisition one (EQ_ALGO=0) or the tracking one (EQ_ALGO=1).

CARLOCK

CARLOCK goes high when the demodulator part within the VES1820X is

synchronized : carrier has been recovered, else CARLOCK is low.

FSYNC

FSYNC goes high when the deinterleaver within the VES1820X is synchronized :

α consecutives MPEG2 sync pattern (or sync ) have been detected. FSYNC goes

low when

β consecutives MPEG2 sync pattern (or sync ) have been missed. α

and

β are programmable within CONF register.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935264539557 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 935266871557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

| 935266917557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

| 935268386557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

| 935267050025 | SPECIALTY CONSUMER CIRCUIT, UUC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。