- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36339 > 935264530157 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | 935264530157 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 封裝: | SOT-317, MQFP-100 |

| 文件頁數(shù): | 20/43頁 |

| 文件大小: | 254K |

| 代理商: | 935264530157 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

1999 March 01

27

Philips Semiconductors

Product specication

Single chip DVB-C channel receiver

VES1820X

FEL

Front End Lock. FEL goes high when the 2 signals CARLOCK and FSYNC are

both at a high level : VES1820X is synchronized according to the DVB

specifications.

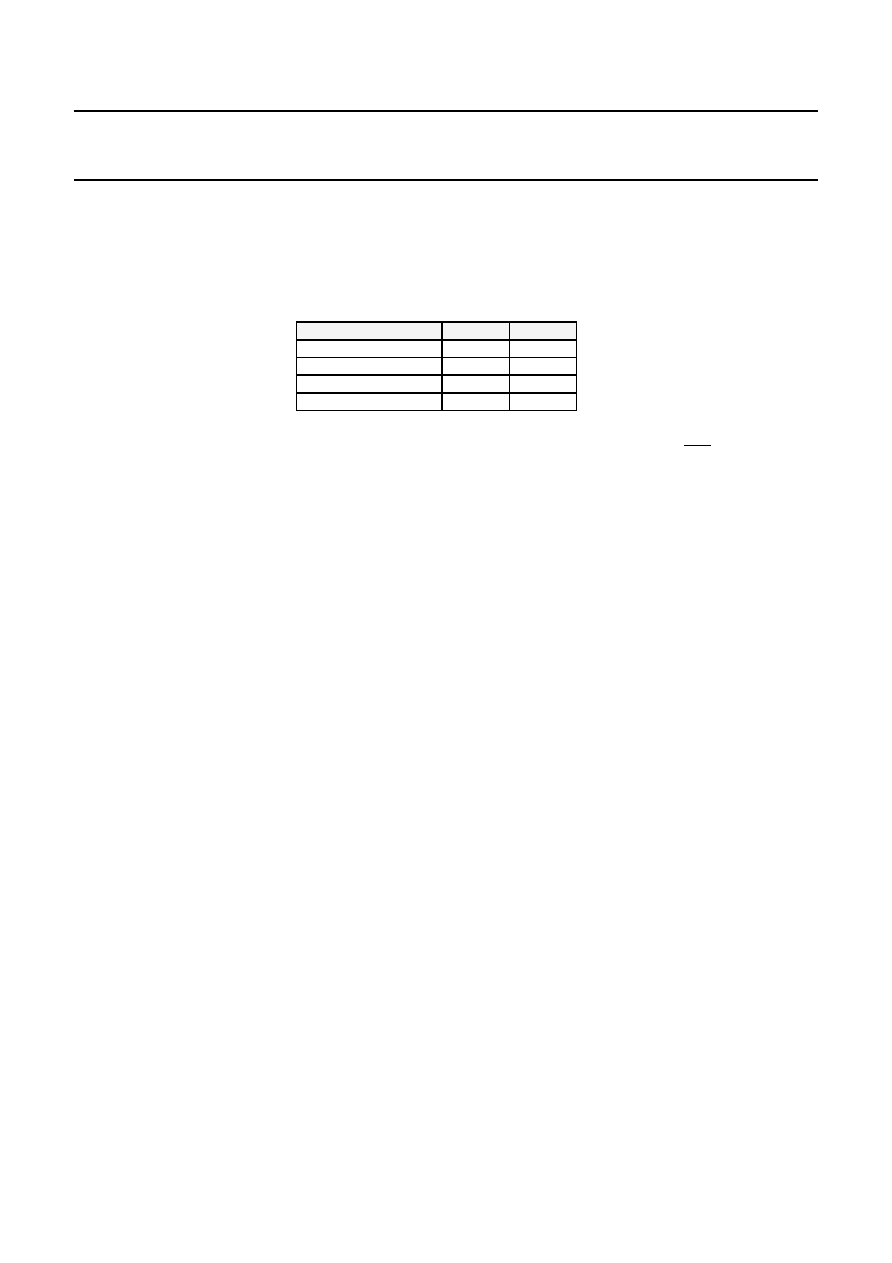

BER[1:0]

BER[1:0] gives a rough idea of the Bit Error Rate at the demodulator output

BER[1:0] determines 4 areas of BER as shown in the following table :

BER

BER[1]

BER[0]

> 10

-2

00

10

-3 < BER < 10-3

01

10

-4 < BER < 10-3

10

< 10

-4

11

NODVB

When high this means that the deinterleaver has been able to synchronize in DVB

mode but the framing is not DVB compliant (there is no

sync byte every 8

frames).

19. POLA

12

16

READ/WRITE

POCLK

Determines if the VES1820X output clock OCLK is inverted or not. When POCLK

is set low (default), the OCLK clock is not inverted, and the falling edge of the

clock is located in the middle of the provided DO[7:0] byte. When POCLK is set

high, then the rising edge of the clock is located in the middle of the DO[7:0]

output byte.

PDEN

Determines if the VES1820X output signal DEN is inverted or not before being

provided. When set low (default), DEN is not inverted and therefore is high during

the 188 first bytes of each packet and low for the 16 remaining bytes. When set

high DEN is low for 188 bytes and high for 16.

PUNCOR

Determines if the VES1820X output signal UNCOR is inverted or not before being

provided. When set low (default), UNCOR is not inverted and therefore is high

during the 188 first bytes of each packet and low for the 16 remaining bytes only

in case where the provided packet is declared uncorrectable by the RS decoder. If

the packet is correctable UNCOR remains low for the 204 bytes. When set high,

UNCOR is low for 188 bytes and high for 16, always in case of an uncorrectable

packet. If the packet is correctable UNCOR remains high for the 204 bytes of the

packet.

PPSYNC

Determines if the VES1820X output signal PSYNC is inverted or not before being

provided. When set low (default), PSYNC output signal is not inverted and

therefore is high during the first byte of each packet (sync byte 47

16

and low for

the 203 remaining bytes. When set high, PSYNC is low for the first byte of each

packet (sync byte 47

16

) and high for 203 remaining bytes.

PFEL

Determines if the VES1820X output signal FEL is inverted or not before being

provided. When set low (default) FEL is not inverted and is high when the

VES1820X is fully synchronized. When set high, FEL is inverted and is low when

the VES1820X is fully synchronized.

P/MF

Determines whether the PSYNC or MFSTART signal is provided on the PSYNC

output pin of the VES1820X. When set high (default), PSYNC is provided. When

set low, MFSTART is provided. MFSTART corresponds to the detection of the

inverted sync byte B8

16

: MFSTART is high one frame out of eight for a period of

OCLK at the beginning of the packet.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935264533557 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 935264539557 | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| 935266871557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

| 935266917557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

| 935268386557 | SPECIALTY CONSUMER CIRCUIT, PBGA292 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

| 935269544557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY TDA9587-2US1-V1.3 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。