- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360436 > 74F50109 (NXP Semiconductors N.V.) Synchronizing dual J-K positive edge-triggered flip-flop with metastable immune characteristics PDF資料下載

參數(shù)資料

| 型號: | 74F50109 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Synchronizing dual J-K positive edge-triggered flip-flop with metastable immune characteristics |

| 中文描述: | 同步雙JK正沿觸發(fā)器與亞穩(wěn)態(tài)觸發(fā)器免疫特性 |

| 文件頁數(shù): | 2/12頁 |

| 文件大小: | 97K |

| 代理商: | 74F50109 |

Philips Semiconductors

Product specification

74F50109

Synchronizing dual J–K positive edge-triggered

flip-flop with metastable immune characteristics

2

September 14, 1990

853-1388 00422

FEATURE

Metastable immune characteristics

Output skew guaranteed less than 1.5ns

High source current (I

OH

= 15mA) ideal for clock driver

applications

Pinout compatible with 74F109

See 74F5074 for synchronizing dual D-type flip-flop

See 74F50728 for synchronizing cascaded D-type flip-flop

See 74F50729 for synchronizing dual D-type flip-flop with

edge-triggered set and reset

TYPE

TYPICAL f

max

TYPICAL SUPPLY

CURRENT( TOTAL)

74F50109

150MHz

22mA

ORDERING INFORMATION

ORDER CODE

COMMERCIAL RANGE

V

CC

= 5V

±

10%,

T

amb

= 0

°

C to +70

°

C

N74F50109N

DESCRIPTION

PKG DWG #

16–pin plastic DIP

SOT38-4

16–pin plastic SO

N74F50109D

SOT109-1

INPUT AND OUTPUT LOADING

AND FAN OUT TABLE

PINS

DESCRIPTION

74F (U.L.)

HIGH/

LOW

LOAD

VALUE

HIGH/LOW

J0, J1

J inputs

1.0/0.417

20

μ

A/250

μ

A

20

μ

A/250

μ

A

K0, K1

K inputs

1.0/0.417

CP0, CP1

Clock inputs

(active rising edge)

1.0/0.033

20

μ

A/20

μ

A

SD0, SD1

Set inputs

(active low)

1.0/0.033

20

μ

A/20

μ

A

RD0, RD1

Reset inputs

(active low)

1.0/0.033

20

μ

A/20

μ

A

Q0, Q1, Q0, Q1

NOTE:

One (1.0) FAST unit load is defined as: 20

μ

A in the high

state and 0.6mA in the low state.

Data outputs

750/33

15mA/20mA

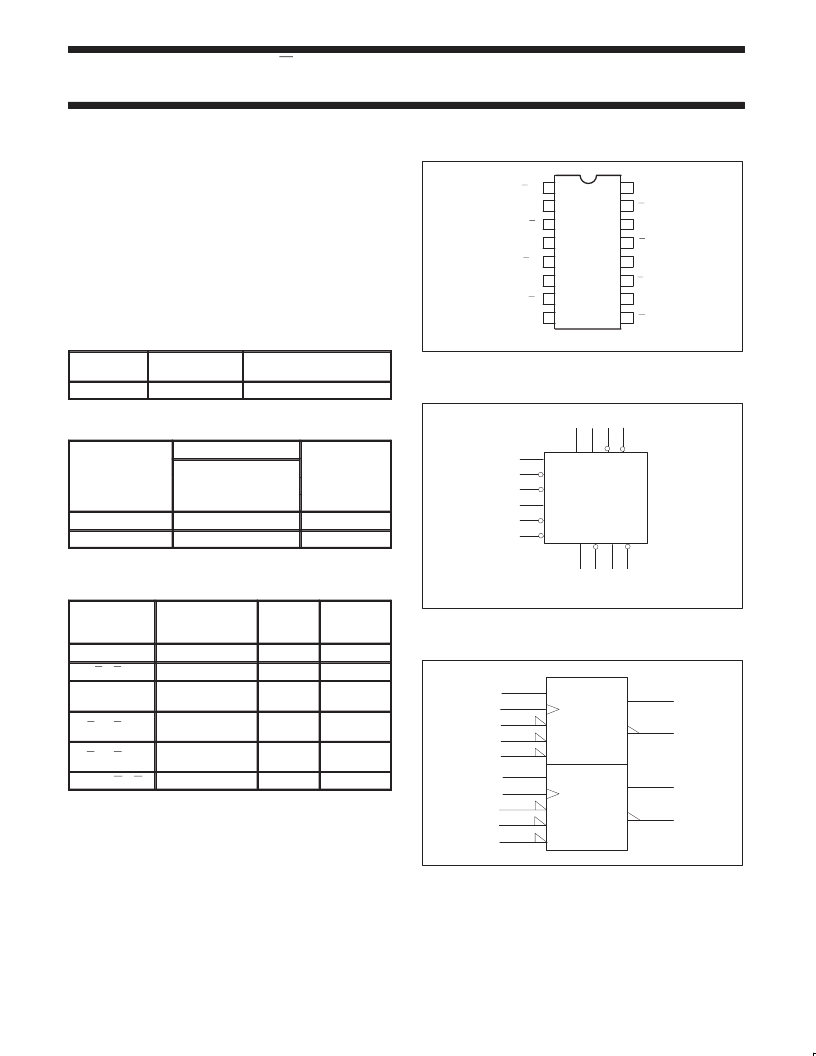

PIN CONFIGURATION

GND

V

CC

SD1

Q1

Q1

CP1

RD1

J1

RD0

J0

CP0

SD0

Q0

Q0

16

15

14

13

12

11

10

7

6

5

4

3

2

1

9

8

K1

K0

SF00598

LOGIC SYMBOL

J1

J0

Q0 Q0 Q1 Q1

V

= Pin 16

GND = Pin 8

CP0

SD0

RD0

CP1

SD1

RD1

4

5

1

12

11

15

K1

K0

2 14 3 13

6 7 10 9

SF00599

IEC/IEEE SYMBOL

6

7

1J

2J

C1

C2

R

1K

2K

R

S

S

10

9

2

4

3

1

5

14

12

13

15

11

SF00600

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F597 | 8-bit shift register with input storage registers(帶輸入存儲寄存的8位移位寄存器(三態(tài))) |

| 74F50728 | Synchronizing cascaded dual positive edge-triggered D-type flip-flop |

| 74F50729 | Synchronizing dual D-type flip-flop with edge-triggered set and reset with metastable immune characteristics |

| 74F5074 | Synchronizing dual D-type flip-flop/clock driver(同步雙D觸發(fā)器/時鐘驅(qū)動器) |

| 74F51SCX | 2/2-input and 3/3-input AND-NOR Gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F50728 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Synchronizing cascaded dual positive edge-triggered D-type flip-flop |

| 74F50729 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Synchronizing dual D-type flip-flop with edge-triggered set and reset with metastable immune characteristics |

| 74F5074 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Synchronizing dual D-type flip-flop/clock driver |

| 74F5074D | 制造商:SGS 功能描述:74F5074 SGS S1I2B 制造商:NXP Semiconductors 功能描述: |

| 74F5074N | 制造商:NXP Semiconductors 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。