- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄18687 > 73S1217F-68M/F/PE (Maxim Integrated)IC SOC SMART CARD READER 68QFN PDF資料下載

參數(shù)資料

| 型號(hào): | 73S1217F-68M/F/PE |

| 廠商: | Maxim Integrated |

| 文件頁(yè)數(shù): | 13/140頁(yè) |

| 文件大?。?/td> | 0K |

| 描述: | IC SOC SMART CARD READER 68QFN |

| 標(biāo)準(zhǔn)包裝: | 260 |

| 系列: | * |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)

DS_1217F_002

73S1217F Data Sheet

Rev. 1.2

11

1.2 Hardware Overview

The 73S1217F single smart card controller integrates all primary functional blocks required to implement

a smart card reader with host serial and / or USB interface. Included on chip are an 8051-compatible

microprocessor (MPU) which executes up to one instruction per clock cycle (80515), a fully integrated IS0

7816 compliant smart card interface, expansion smart card interface, full speed USB 2.0 compatible

interface, serial interface, I2C interface, 6 x 5 keypad interface, RAM, FLASH memory, a real time clock

(RTC), and a variety of I/O pins.

Advanced power management features include a DC-DC converter and on-chip regulators that generate

all the necessary voltages for the circuit: Primarily a smart card supply VCC, (selectable to 1.8V, 3V or

5V) and a 3.3V digital voltage output (VDD, pin #68) that must be connected to the power supply inputs of

the digital core of the circuit, pins # 28 and 40 (these are not internally connected). Should external

circuitry require a 3.3V digital power supply, the VDD output is capable of supplying additional current.

The whole IC can be powered up either from a USB bus-power supply (VBUS +5V typical), or from a

typical set of battery cells VBAT. Automated switching between these supply inputs give the priority to

VBUS to save the battery life.

A functional block diagram of the 73S1217F is shown in Figure 1.

1.3 80515 MPU Core

1.3.1 80515 Overview

The 73S1217F includes an 80515 MPU (8-bit, 8051-compatible) that performs most instructions in one

clock cycle. The 80515 architecture eliminates redundant bus states and implements parallel execution

of fetch and execution phases. Normally a machine cycle is aligned with a memory fetch, therefore, most

of the 1-byte instructions are performed in a single cycle. This leads to an 8x performance (average)

improvement (in terms of MIPS) over the Intel 8051 device running at the same clock frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application

(cryptographic calculations, key management, memory management, and I/O management) using the

XRAM special function register MPUCKCtl.

Typical smart card, USB, serial, keyboard, I2C and RTC management functions are available for the

MPU as part of the Teridian standard library. A standard ANSI “C” 80515-application programming

interface library is available to help reduce design cycle. Refer to the 73S12xxF Software User’s Guide.

1.3.2 Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces.

Memory organization in the 80515 is similar to that of the industry standard 8051. There are three

memory areas: Program memory (Flash), external data memory (XRAM), and internal data memory

(IRAM). Data bus address space is allocated to on-chip memory as shown Table 2.

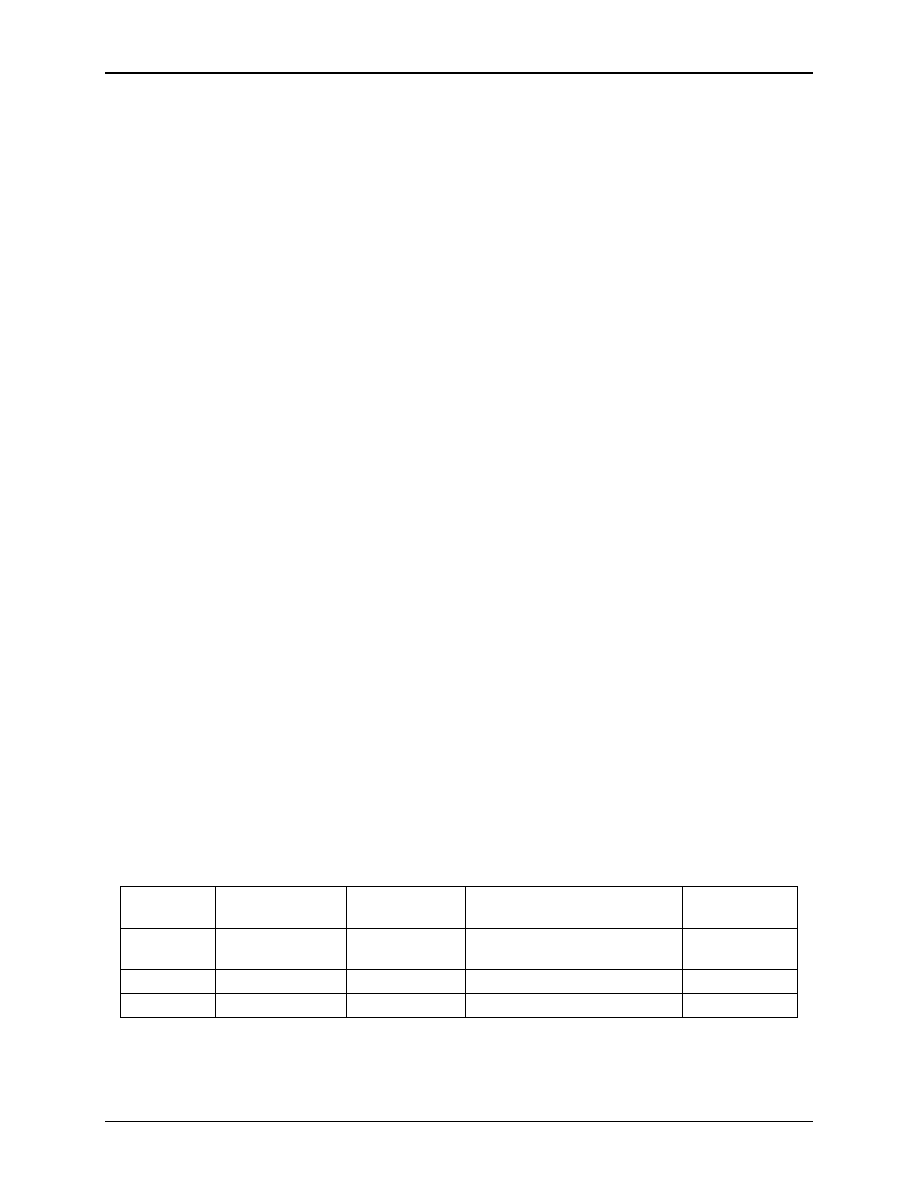

Table 2: MPU Data Memory Map

Address

(hex)

Memory

Technology

Memory Type

Typical Usage

Memory Size

(bytes)

0000-FFFF

Flash Memory

Non-volatile

Program and non-volatile

data

64KB

0000-07FF

Static RAM

Volatile

MPU data XRAM

2KB

FC00-FFFF

External SFR

Volatile

Peripheral control

1KB

Note: The IRAM is part of the core and is addressed differently.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 73S1210F-68M/F/PH | IC SOC SMART CARD READER 68QFN |

| 73S1210F-68M/F/PG | IC SOC SMART CARD READER 68QFN |

| 73S1210F-68MR/F/PH | IC SOC SMART CARD READER 68QFN |

| FQD1N80TM | MOSFET N-CH 800V 1A DPAK |

| 73S1210F-68MR/F/PG | IC SOC SMART CARD READER 68QFN |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 73S1217F-68MR/F/PE | 功能描述:8位微控制器 -MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線(xiàn)寬度:8 bit 最大時(shí)鐘頻率:50 MHz 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| 73S1217F-EB | 功能描述:開(kāi)發(fā)板和工具包 - 8051 73S1217F Eval Brd (Usb Cable, Doc. Cd) RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類(lèi)型:USB 工作電源電壓: |

| 73S1217F-EB-Lite | 功能描述:開(kāi)發(fā)板和工具包 - 8051 73S1217F EVB Lite w/Plug & Play/Usb RoHS:否 制造商:Silicon Labs 產(chǎn)品:Development Kits 工具用于評(píng)估:C8051F960, Si7005 核心: 接口類(lèi)型:USB 工作電源電壓: |

| 73S1217F-IMR/F | 制造商:TERIDIAN 制造商全稱(chēng):TERIDIAN 功能描述:Bus-Powered 80515 System-on-Chip with USB, ISO 7816 / EMV, PINpad and More |

| 73S13B | 制造商:QUARTZCOM 制造商全稱(chēng):QUARTZCOM the communications company 功能描述:-20 ~ +70 °C commercia l application -30 ~ +75 °C on request |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。