- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄250212 > 70V659S10DR (INTEGRATED DEVICE TECHNOLOGY INC) 128K X 36 DUAL-PORT SRAM, 10 ns, PQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | 70V659S10DR |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | SRAM |

| 英文描述: | 128K X 36 DUAL-PORT SRAM, 10 ns, PQFP208 |

| 封裝: | 28 X 28 MM, 3.50 MM HEIGHT, PLASTIC, QFP-208 |

| 文件頁(yè)數(shù): | 5/24頁(yè) |

| 文件大?。?/td> | 316K |

| 代理商: | 70V659S10DR |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)

13

IDT70V659/58/57S

High-Speed 3.3V 128/64/32K x 36 Asynchronous Dual-Port Static RAM

Industrial and Commercial Temperature Ranges

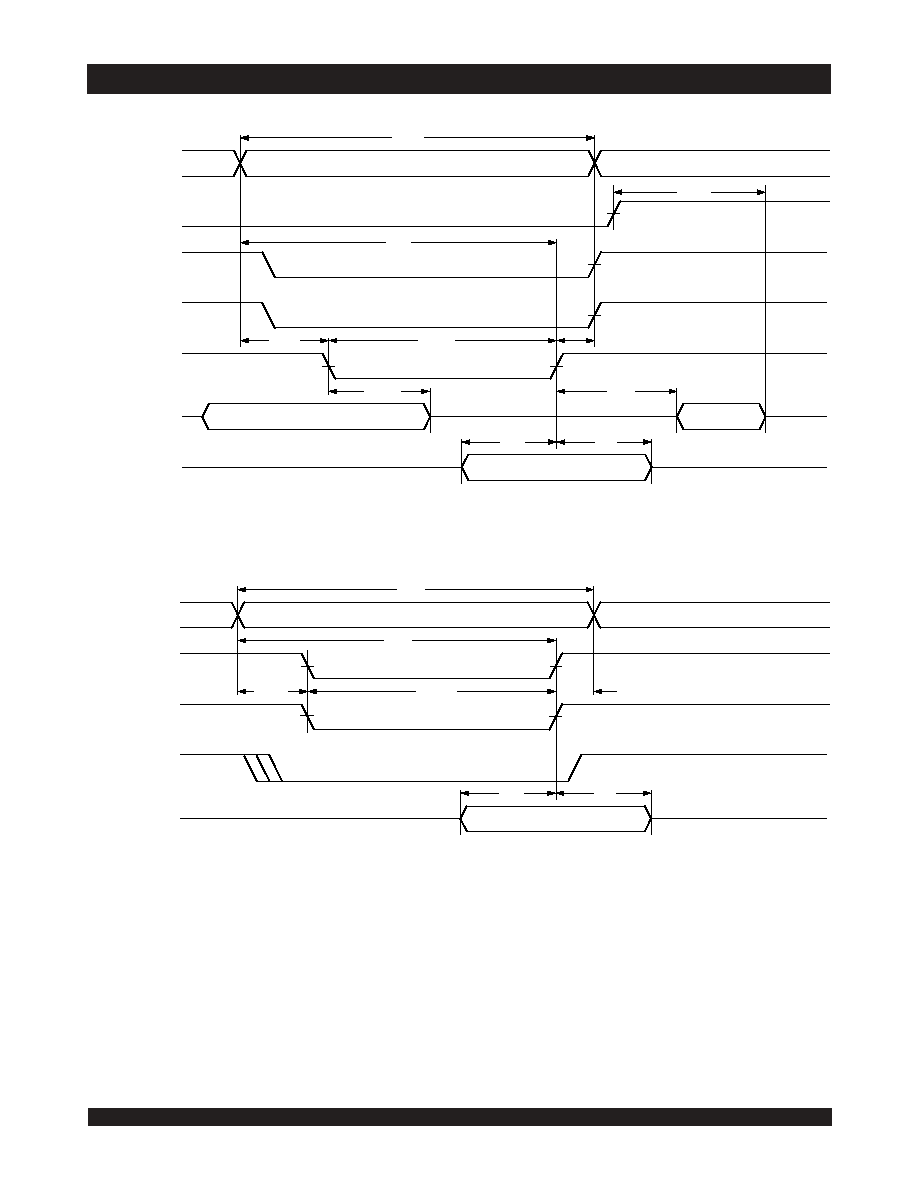

Timing Waveform of Write Cycle No. 1, R/W Controlled Timing(1,5,8)

Timing Waveform of Write Cycle No. 2, CE Controlled Timing(1,5)

NOTES:

1. R/W or CE or BEn = VIH during all address transitions.

2. A write occurs during the overlap (tEW or tWP) of a CE = VIL and a R/W = VIL for memory array writing cycle.

3. tWR is measured from the earlier of CE or R/W (or SEM or R/W) going HIGH to the end of write cycle.

4. During this period, the I/O pins are in the output state and input signals must not be applied.

5. If the CE or SEM = VIL transition occurs simultaneously with or after the R/W = VIL transition, the outputs remain in the High-impedance state.

6. Timing depends on which enable signal is asserted last, CE or R/W.

7. This parameter is guaranteed by device characterization, but is not production tested. Transition is measured 0mV from steady state with the Output Test Load

(Figure 2).

8. If OE = VIL during R/W controlled write cycle, the write pulse width must be the larger of tWP or (tWZ + tDW) to allow the I/O drivers to turn off and data to be

placed on the bus for the required tDW. If OE = VIH during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the

specified tWP.

9. To access RAM, CE = VIL and SEM = VIH. To access semaphore, CE = VIH and SEM = VIL. tEW must be met for either condition.

R/

W

tWC

tHZ

tAW

tWR

tAS

tWP

DATAOUT

(2)

tWZ

tDW

tDH

tOW

OE

ADDRESS

DATAIN

(6)

(4)

(7)

BEn

4869 drw 08

(9)

CE or SEM

(9)

(7)

(3)

4869 drw 09

tWC

tAS

tWR

tDW

tDH

ADDRESS

DATAIN

R/

W

tAW

tEW

BEn

(3)

(2)

(6)

CE or SEM

(9)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 7P12FLV262C25 | 6M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

| 7P12FLV520I15 | 6M X 16 FLASH 3V PROM CARD, 150 ns, XMA68 |

| 7P24FLV251I25 | 12M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

| 7P24FLV280I15 | 12M X 16 FLASH 3V PROM CARD, 150 ns, XMA68 |

| 7P24FLV570I25 | 12M X 16 FLASH 3V PROM CARD, 250 ns, XMA68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 70V659S10DRG | 功能描述:IC SRAM 4MBIT 208QFP 制造商:idt, integrated device technology inc 系列:* 零件狀態(tài):在售 標(biāo)準(zhǔn)包裝:6 |

| 70V659S12BC | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 3.3V 4.5M-Bit 128K x 36 12ns 256-Pin CABGA Tray 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 4.5MBIT 128KX36 12NS 256BGA - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:128Kx36 STD-PWR 3.3V DUAL-PORT RAM |

| 70V659S12BC8 | 制造商:Integrated Device Technology Inc 功能描述:SRAM Chip Async Dual 3.3V 4.5M-Bit 128K x 36 12ns 256-Pin CABGA T/R 制造商:Integrated Device Technology Inc 功能描述:SRAM ASYNC DUAL 3.3V 4.5MBIT 128KX36 12NS 256BGA - Tape and Reel 制造商:Integrated Device Technology Inc 功能描述:128Kx36 STD-PWR 3.3V DUAL-PORT RAM |

| 70V659S12BCGI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 128Kx36 STD-PWR 3.3V DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

| 70V659S12BCI | 功能描述:靜態(tài)隨機(jī)存取存儲(chǔ)器 128Kx36 STD-PWR 3.3V DUAL-PORT RAM RoHS:否 制造商:Cypress Semiconductor 存儲(chǔ)容量:16 Mbit 組織:1 M x 16 訪問(wèn)時(shí)間:55 ns 電源電壓-最大:3.6 V 電源電壓-最小:2.2 V 最大工作電流:22 uA 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:TSOP-48 封裝:Tray |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。