- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4257 > XCV50E-7PQ240I (Xilinx Inc)IC FPGA 1.8V I-TEMP 240-PQFP PDF資料下載

參數(shù)資料

| 型號: | XCV50E-7PQ240I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 43/233頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 1.8V I-TEMP 240-PQFP |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Virtex®-E |

| LAB/CLB數(shù): | 384 |

| 邏輯元件/單元數(shù): | 1728 |

| RAM 位總計(jì): | 65536 |

| 輸入/輸出數(shù): | 158 |

| 門數(shù): | 71693 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 240-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 240-PQFP(32x32) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁當(dāng)前第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁

Virtex-E 1.8 V Field Programmable Gate Arrays

R

DS022-4 (v3.0) March 21, 2014

Module 4 of 4

Production Product Specification

51

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

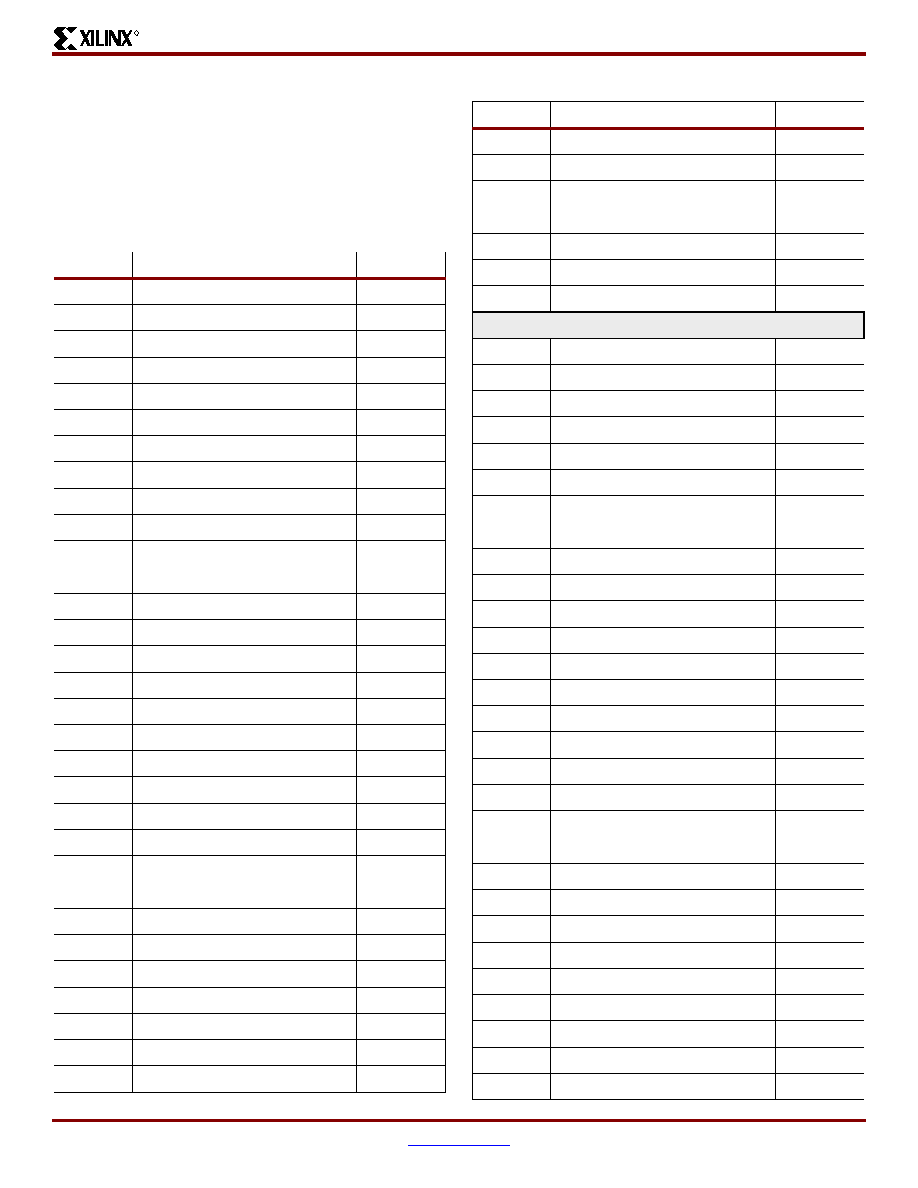

FG456 Fine-Pitch Ball Grid Array Packages

XCV200E and XCV300E devices in FG456 fine-pitch Ball

Grid Array packages have footprint compatibility. Pins

labeled I0_VREF can be used as either in both devices pro-

vided in this package. If the pin is not used as VREF, it can be

used as general I/O. Immediately following Table 18, see

Table 19 for Differential Pair information.

Table 18: FG456 — XCV200E and XCV300E

Bank

Pin Description

Pin #

0GCK3

C11

0IO

A21

0IO

A3

0IO

A61

0IO

A10

0IO

B5

0IO

B9

0IO

C5

0IO

D8

0IO

D10

0IO

E111

0IO_L0N

D5

0IO_L0P

B3

0

IO_VREF_L1N_YY

B4

0

IO_L1P_YY

E6

0IO_L2N

A4

0IO_L2P

E7

0

IO_VREF_L3N_YY

C6

0

IO_L3P_YY

D6

0IO_L4N_Y

A5

0

IO_L4P_Y

B6

0IO_L5N_Y

D7

0

IO_L5P_Y

C7

0

IO_VREF_L6N_YY

E8

0

IO_L6P_YY

B7

0

IO_L7N_YY

A7

0

IO_L7P_YY

E9

0IO_L8N_Y

C8

0

IO_L8P_Y

B8

0IO_L9N_Y

D9

0

IO_L9P_Y

A8

0

IO_L10N

C9

0

IO_L10P

E10

0

IO_VREF_L11N_YY

A9

0

IO_L11P_YY

C10

0

IO_L12N_Y

F11

0

IO_L12P_Y

B10

0

IO_LVDS_DLL_L13N

B11

1GCK2

A11

1IO

A121

1IO

A14

1IO

B161

1IO

B19

1IO

E13

1IO

E15

1IO

E16

1IO

E171

1

IO_LVDS_DLL_L13P

D11

1

IO_L14N_Y

C12

1

IO_L14P_Y

D12

1

IO_L15N_Y

B12

1

IO_L15P_Y

A13

1

IO_L16N_YY

E12

1

IO_VREF_L16P_YY

B13

1

IO_L17N_YY

C13

1

IO_L17P_YY

D13

1

IO_L18N_Y

B14

1

IO_L18P_Y

C14

1

IO_L19N_Y

F12

1

IO_L19P_Y

A15

1

IO_L20N_YY

B15

1

IO_L20P_YY

C15

1

IO_L21N_YY

A16

1

IO_VREF_L21P_YY

E14

1

IO_L22N_Y

D14

1

IO_L22P_Y

C16

1

IO_L23N_Y

D15

Table 18: FG456 — XCV200E and XCV300E

Bank

Pin Description

Pin #

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASM43DRMN | CONN EDGECARD 86POS .156 WW |

| AGM43DRMN | CONN EDGECARD 86POS .156 WW |

| AYM43DRMH | CONN EDGECARD 86POS .156 WW |

| ASM43DRMH | CONN EDGECARD 86POS .156 WW |

| AGM43DRMH | CONN EDGECARD 86POS .156 WW |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV50E-7PQG240C | 制造商:Xilinx 功能描述:IC SYSTEM GATE 制造商:Xilinx 功能描述:FPGA VIRTEX-E 20.736K GATES 1728 CELLS 400MHZ 0.18UM 1.8V 24 - Trays |

| XCV50E-8BG240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV50E-8BG240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV50E-8CS144C | 功能描述:IC FPGA 1.8V C-TEMP 144-CSBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Virtex®-E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XCV50E-8CS144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。