- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4208 > XC6VCX240T-2FFG784I (Xilinx Inc)IC FPGA VIRTEX 6 241K 784FFGBGA PDF資料下載

參數(shù)資料

| 型號: | XC6VCX240T-2FFG784I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 32/52頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA VIRTEX 6 241K 784FFGBGA |

| 產(chǎn)品培訓(xùn)模塊: | Virtex-6 FPGA Overview |

| 產(chǎn)品變化通告: | Virtex-6 FIFO Input Logic Reset 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex® 6 CXT |

| LAB/CLB數(shù): | 18840 |

| 邏輯元件/單元數(shù): | 241152 |

| RAM 位總計: | 15335424 |

| 輸入/輸出數(shù): | 400 |

| 電源電壓: | 0.95 V ~ 1.05 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 784-BBGA,F(xiàn)CBGA |

| 供應(yīng)商設(shè)備封裝: | 784-FCBGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁

Virtex-6 CXT Family Data Sheet

DS153 (v1.6) February 11, 2011

Product Specification

38

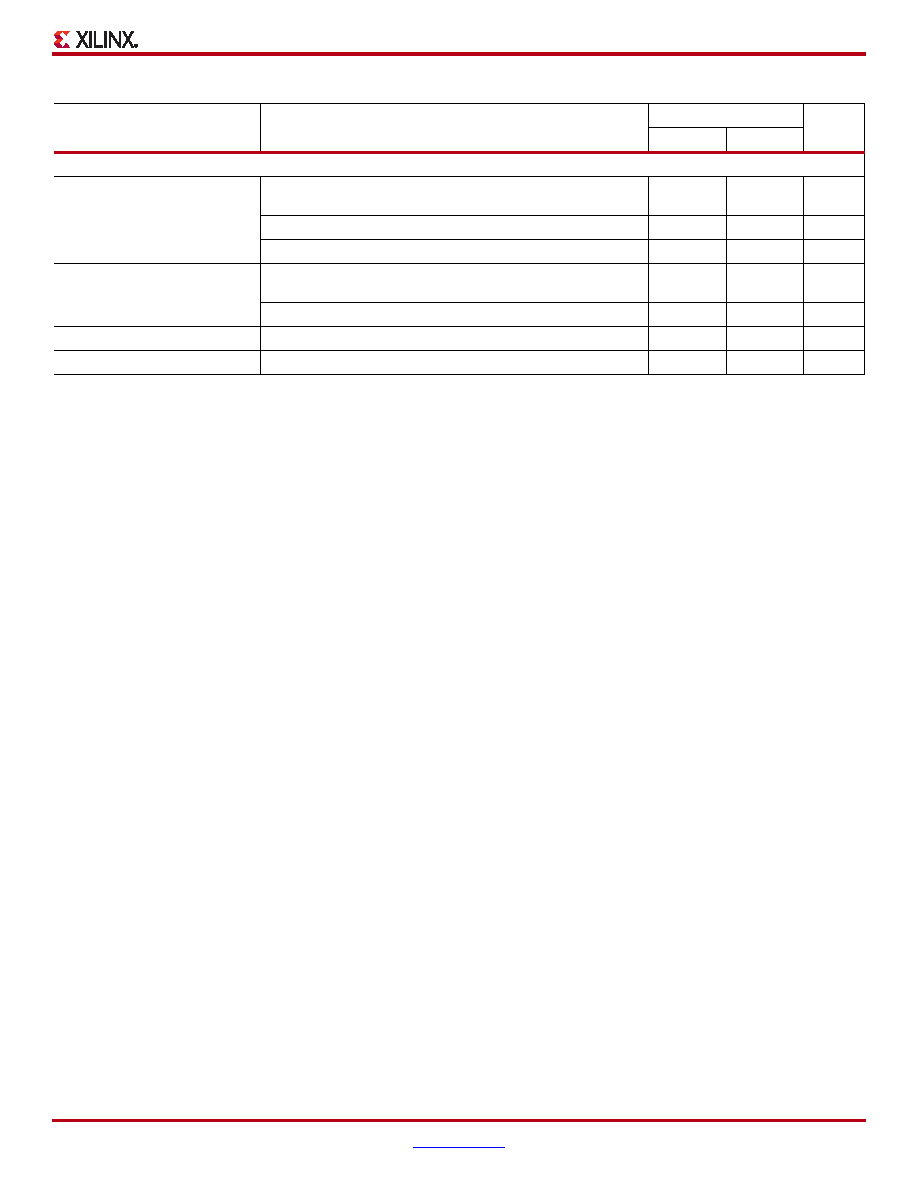

Maximum Frequency

FMAX

Block RAM

(Write First and No Change modes)

400

350

MHz

Block RAM (Read First mode)

400

347

MHz

Block RAM (SDP mode)(12)

400

347

MHz

FMAX_CASCADE

Block RAM Cascade

(Write First and No Change modes)

400

347

MHz

Block RAM Cascade (Read First mode)

350

304

MHz

FMAX_FIFO

FIFO in all modes

400

350

MHz

FMAX_ECC

Block RAM and FIFO in ECC configuration

325

282

MHz

Notes:

1.

TRACE will report all of these parameters as TRCKO_DO.

2.

TRCKO_DOR includes TRCKO_DOW, TRCKO_DOPR, and TRCKO_DOPW as well as the B port equivalent timing parameters.

3.

These parameters also apply to synchronous FIFO with DO_REG = 0.

4.

TRCKO_DO includes TRCKO_DOP as well as the B port equivalent timing parameters.

5.

These parameters also apply to multirate (asynchronous) and synchronous FIFO with DO_REG = 1.

6.

TRCKO_FLAGS includes the following parameters: TRCKO_AEMPTY, TRCKO_AFULL, TRCKO_EMPTY, TRCKO_FULL, TRCKO_RDERR, TRCKO_WRERR.

7.

TRCKO_POINTERS includes both TRCKO_RDCOUNT and TRCKO_WRCOUNT.

8.

The ADDR setup and hold must be met when EN is asserted (even when WE is deasserted). Otherwise, block RAM data corruption is

possible.

9.

TRCKO_DI includes both A and B inputs as well as the parity inputs of A and B.

10. TRCO_FLAGS includes the following flags: AEMPTY, AFULL, EMPTY, FULL, RDERR, WRERR, RDCOUNT, and WRCOUNT.

11. The FIFO reset must be asserted for at least three positive clock edges.

12. When using ISE software v12.4 or later, if the RDARRDR_COLLISION_HWCONFIG attribute is set to PERFORMANCE or the block RAM

is in single-port operation, then the faster FMAX for WRITE_FIRST/NO_CHANGE modes apply.

Table 50: Block RAM and FIFO Switching Characteristics (Cont’d)

Symbol

Description

Speed Grade

Units

-2

-1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ABB106DHHN-S621 | CONN EDGECARD 212PS .050 DIP SLD |

| ABB106DHHD-S621 | CONN EDGECARD 212PS .050 DIP SLD |

| XC2V3000-5FF1152I | IC FPGA VIRTEX-II 1152FCBGA |

| ACB106DHHN-S578 | EDGECARD 212POS .050 SLD W/POSTS |

| XC5VFX70T-2FF1136I | IC FPGA VIRTEX-5FXT 1136FFBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC6VCX75T | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-6 CXT Family Data Sheet |

| XC6VCX75T-1FF484C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 74496 CELLS 40NM (CMOS) TECHNOLOGY - Trays 制造商:Xilinx 功能描述:IC FPGA VIRTEX 6 75K 484BGA |

| XC6VCX75T-1FF484I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 74496 CELLS 40NM (CMOS) TECHNOLOGY - Trays 制造商:Xilinx 功能描述:IC FPGA 240 I/O 484FCBGA |

| XC6VCX75T-1FF784C | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 74496 CELLS 40NM (CMOS) TECHNOLOGY - Trays 制造商:Xilinx 功能描述:IC FPGA 360 I/O 784FCBGA |

| XC6VCX75T-1FF784I | 制造商:Xilinx 功能描述:FPGA VIRTEX?-6 CXT FAMILY 74496 CELLS 40NM (CMOS) TECHNOLOGY - Trays 制造商:Xilinx 功能描述:IC FPGA 360 I/O 784FCBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。