- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4176 > XC3042A-7PQ100C (Xilinx Inc)IC LOGIC CL ARRAY 4200GAT 100PQF PDF資料下載

參數(shù)資料

| 型號: | XC3042A-7PQ100C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 76/76頁 |

| 文件大小: | 0K |

| 描述: | IC LOGIC CL ARRAY 4200GAT 100PQF |

| 產(chǎn)品變化通告: | Product Discontinuation 27/Apr/2010 |

| 標準包裝: | 1 |

| 系列: | XC3000A/L |

| LAB/CLB數(shù): | 144 |

| RAM 位總計: | 30784 |

| 輸入/輸出數(shù): | 82 |

| 門數(shù): | 3000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-BQFP |

| 供應商設備封裝: | 100-QFP(14x20) |

| 其它名稱: | 122-1026 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當前第76頁

R

November 9, 1998 (Version 3.1)

7-11

XC3000 Series Field Programmable Gate Arrays

7

General Purpose Interconnect

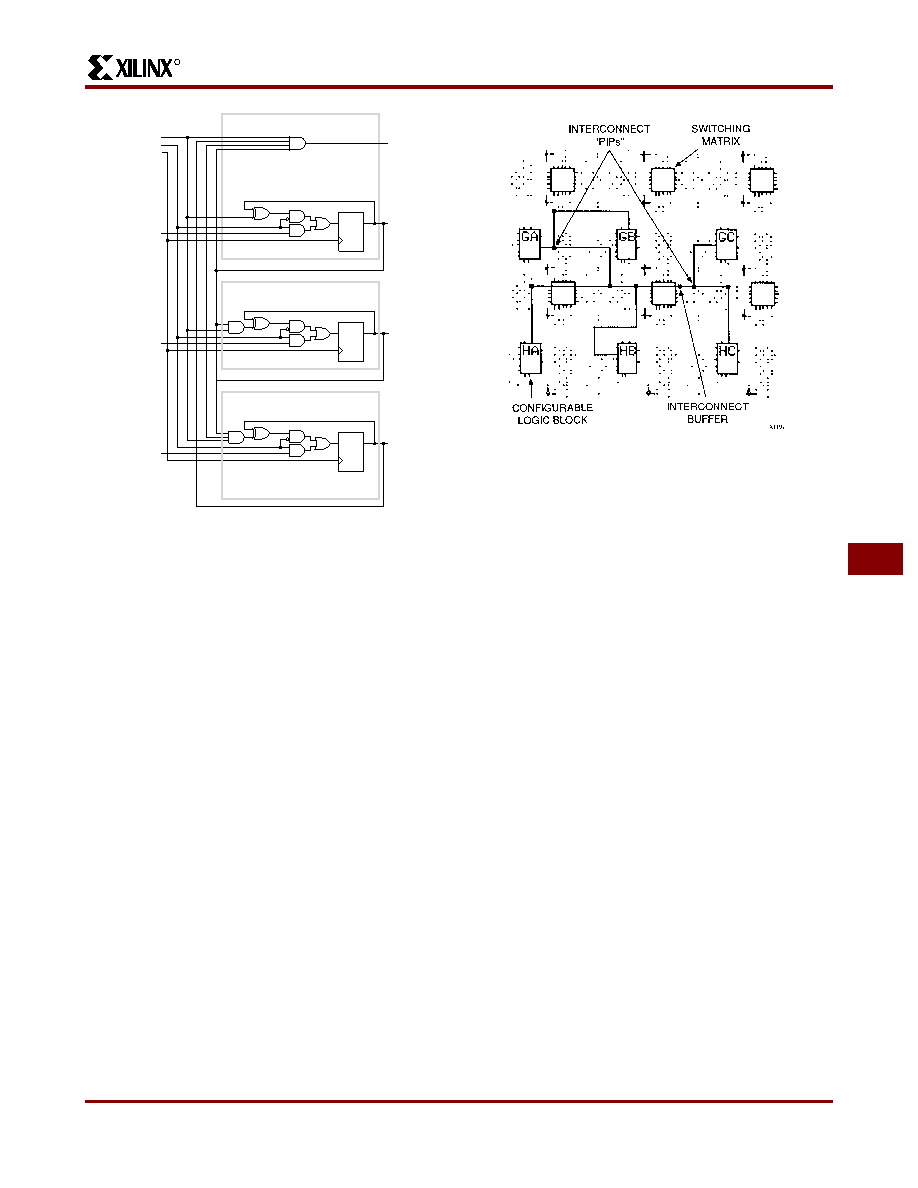

General purpose interconnect, as shown in Figure 10, con-

sists of a grid of five horizontal and five vertical metal seg-

ments located between the rows and columns of logic and

IOBs. Each segment is the height or width of a logic block.

Switching matrices join the ends of these segments and

allow programmed interconnections between the metal grid

segments of adjoining rows and columns. The switches of

an unprogrammed device are all non-conducting. The con-

nections through the switch matrix may be established by

the automatic routing or by selecting the desired pairs of

matrix pins to be connected or disconnected. The legiti-

mate switching matrix combinations for each pin are indi-

cated in Figure 11.

Special buffers within the general interconnect areas pro-

vide periodic signal isolation and restoration for improved

performance of lengthy nets. The interconnect buffers are

available to propagate signals in either direction on a given

general interconnect segment. These bidirectional (bidi)

buffers are found adjacent to the switching matrices, above

and to the right. The other PIPs adjacent to the matrices

are accessed to or from Longlines. The development sys-

tem automatically defines the buffer direction based on the

location of the interconnection network source. The delay

calculator of the development system automatically calcu-

lates and displays the block, interconnect and buffer delays

for any paths selected. Generation of the simulation netlist

with a worst-case delay model is provided.

Direct Interconnect

Direct interconnect, shown in Figure 12, provides the most

efficient implementation of networks between adjacent

CLBs or I/O Blocks. Signals routed from block to block

using the direct interconnect exhibit minimum interconnect

propagation and use no general interconnect resources.

For each CLB, the X output may be connected directly to

the B input of the CLB immediately to its right and to the C

input of the CLB to its left. The Y output can use direct inter-

connect to drive the D input of the block immediately above

and the A input of the block below. Direct interconnect

should be used to maximize the speed of high-performance

portions of logic. Where logic blocks are adjacent to IOBs,

direct connect is provided alternately to the IOB inputs (I)

and outputs (O) on all four edges of the die. The right edge

provides additional direct connects from CLB outputs to

adjacent IOBs. Direct interconnections of IOBs with CLBs

are shown in Figure 13.

D

Q

D

Q

D

Q

Count Enable

Parallel Enable

Clock

D2

D1

D0

Dual Function of 4 Variables

Function of 6 Variables

Function of 5 Variables

Q2

Q1

Q0

FG

Mode

F

Mode

FGM

Mode

Terminal

Count

X5383

Figure 7: Counter.

The modulo-8 binary counter with parallel enable and

clock enable uses one combinatorial logic block of each

option.

Figure 8: A Design Editor view of routing resources

used to form a typical interconnection network from

CLB GA.

Product Obsolete or Under Obsolescence

相關PDF資料 |

PDF描述 |

|---|---|

| ABC65DRES-S734 | CONN EDGECARD 130PS .100 EYELET |

| A14V40A-PQG160C | IC FPGA 4K GATES 3.3V 160-PQFP |

| EMC18DTEF | CONN EDGECARD 36POS .100 EYELET |

| A1425A-1PQ160I | IC FPGA 2500 GATES 160-PQFP |

| A1440A-PQG160I | IC FPGA 4K GATES 160-PQFP |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC3042A-7PQ100C0167 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0262 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100C0341 | 制造商:Xilinx 功能描述: |

| XC3042A-7PQ100I | 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC3042A-7PQG100I | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。