- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383980 > UPD16879 (NEC Corp.) MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT PDF資料下載

參數(shù)資料

| 型號: | UPD16879 |

| 廠商: | NEC Corp. |

| 英文描述: | MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| 中文描述: | 單片四H橋驅(qū)動電路 |

| 文件頁數(shù): | 23/32頁 |

| 文件大?。?/td> | 199K |

| 代理商: | UPD16879 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

Data Sheet S14188EJ1V0DS00

23

μ

PD16879

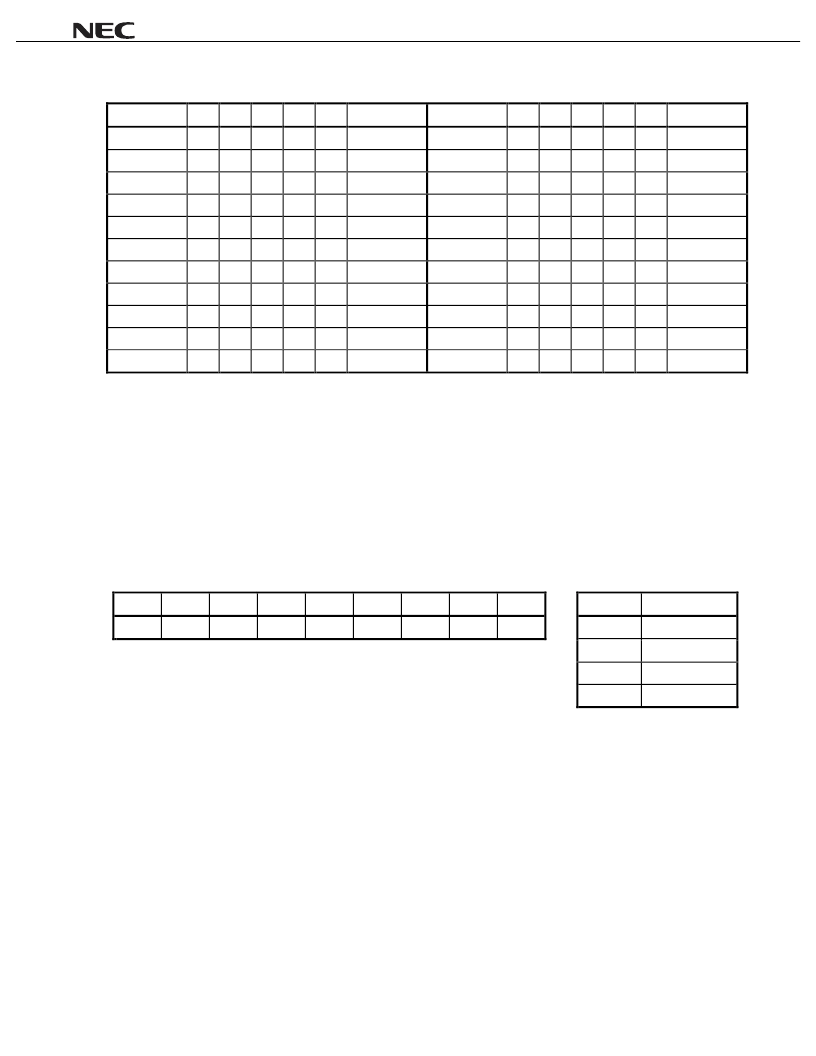

Table 13. Output Current Setting Reference Voltage Data (

β

channel data)

EVR setting

D4

D3

D2

D1

D0

FIL pin voltage

EVR setting

D4

D3

D2

D1

D0

FIL pin voltage

50 mV

0

1

0

1

1

100 mV

160 mV

1

0

1

1

0

320 mV

60 mV

0

1

1

0

0

120 mV

170 mV

1

0

1

1

1

340 mV

70 mV

0

1

1

0

1

140 mV

180 mV

1

1

0

0

0

360 mV

80 mV

0

1

1

1

0

160 mV

190 mV

1

1

0

0

1

380 mV

90 mV

0

1

1

1

1

180 mV

200 mV

1

1

0

1

0

400 mV

100 mV

1

0

0

0

0

200 mV

210 mV

1

1

0

1

1

420 mV

110 mV

1

0

0

0

1

220 mV

220 mV

1

1

1

0

0

440 mV

120 mV

1

0

0

1

0

240 mV

230 mV

1

1

1

0

1

460 mV

130 mV

1

0

0

1

1

260 mV

240 mV

1

1

1

1

0

480 mV

140 mV

1

0

1

0

0

280 mV

250 mV

1

1

1

1

1

500 mV

150 mV

1

0

1

0

1

300 mV

Remark

If D0 to D4 bits input “00000” to “01010”, EVR value fixed 50 mV (FIL pin voltage fixed 100 mV).

FIL pin (peak voltage) is output about double of EVR setting value.

[10th byte]

The 10th byte sets pulse number during 1V

D

period of

β

channel. The pulse number setting 1020 pulses

maximum. It is set by eight bits in terms of software. However, the actual circuit uses 10-bit counter with the low-

order two bits fixed to “0”. Therefore, the number of pulses that is actually generated during fall edge of the first point

wait time + first point magnetize wait time (FF2) cycle is the number of pulses input

×

4. The number of pulses can

be set in a range of 0 to 1020 and in units of four pulses.

Table 14. 10th Byte Data Configuration (

β

channel data)

Bit

D7

D6

D5

D4

D3

D2

D1

D0

Data

Pulse number/V

D

Data

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

0 or 1

00000000

0

MSB

LSB

00101001

164

11111111

1020

n

n

×

4

相關PDF資料 |

PDF描述 |

|---|---|

| UPD1703C-011 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

| UPD1703C-013 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

| UPD1703C-014 | PLL FREQUENCY SYMTHESIZER AND CONTROLLER FOR FM AND AM TUNER |

| UPD1703C-015 | PLL FREQUENCY SYMTHESIZER AND CONTROLLER FOR FM/MW/AM TUNER |

| UPD1703C-017 | PHASE LOCKED LOOP FREQUENCY SYNTHESIZER FM/AM DIGITAL TUNING SYSTEM CONTROLLER CMOS LSI |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| UPD16879GS-BGG | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC QUAD H BRIDGE DRIVER CIRCUIT |

| UPD16882 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16882GS | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC CD-ROM/DVD-ROM 3-PHASE SPINDLE MOTOR DRIVER |

| UPD16886 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC 1.5-CHANNEL H BRIDGE DRIVER CIRCUIT FOR CAMERAS |

| UPD16886MA-6A5 | 制造商:NEC 制造商全稱:NEC 功能描述:MONOLITHIC 1.5-CHANNEL H BRIDGE DRIVER CIRCUIT FOR CAMERAS |

發(fā)布緊急采購,3分鐘左右您將得到回復。