- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄359758 > TSC251G2DXXX-24CED IC CYCLONE III FPGA 80K 484 FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | TSC251G2DXXX-24CED |

| 英文描述: | IC CYCLONE III FPGA 80K 484 FBGA |

| 中文描述: | 微控制器 |

| 文件頁(yè)數(shù): | 9/63頁(yè) |

| 文件大小: | 878K |

| 代理商: | TSC251G2DXXX-24CED |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)當(dāng)前第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)

Rev. A - May 7, 1999

9

TSC80251G2D

6. Address Spaces

The TSC80251G2D derivatives implement four different address spaces:

G

On-chip ROM program/code memory (not present in ROMless devices)

G

On-chip RAM data memory

G

Special Function Registers (SFRs)

G

Configuration array

6.1 Program/Code Memory

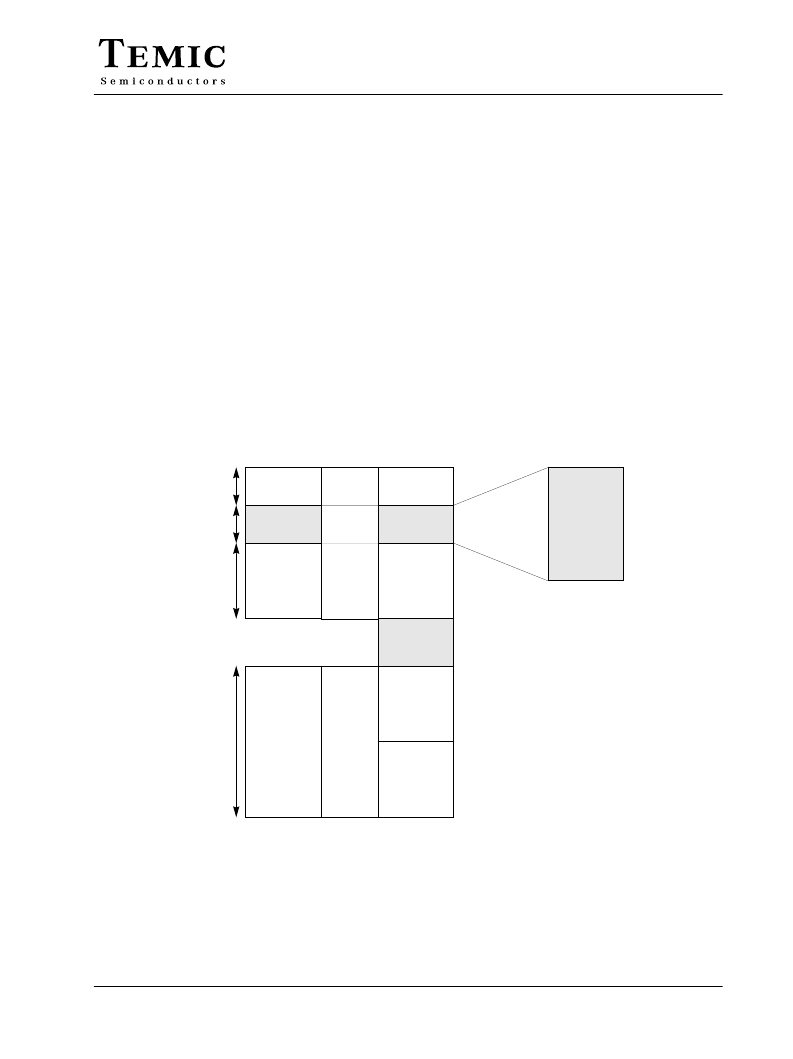

The TSC83251G2D and TSC87251G2D implement 32 Kbytes of on-chip program/code memory. Figure 5 shows

the split of the internal and external program/code memory spaces. If EA# is tied to a high level, the 32-Kbyte

on-chip program memory is mapped in the lower part of segment FF: where the C251 core jumps after reset. The

rest of the program/code memory space is mapped to the external memory. If EA# is tied to a low level, the

internal program/code memory is not used and all the accesses are directed to the external memory.

The TSC83251G2D products provide the internal program/code memory in a masked ROM memory while the

TSC87251G2D products provide it in an EPROM memory. For the TSC80251G2D products, there is no internal

program/code memory and EA# must be tied to a low level.

Figure 5. Program/Code Memory Mapping

Notes:

Special care should be taken when the Program Counter (PC) increments:

1. If the program executes exclusively from on-chip code memory (not from external memory), beware of executing code from the upper eight

bytes of the on-chip ROM (FF:7FF8h-FF:7FFFh). Because of its pipeline capability, the TSC80251G2D derivative may attempt to prefetch

code from external memory (at an address above FF:7FFFh) and thereby disrupt I/O Ports 0 and 2. Fetching code constants from these

8 bytes does not affect Ports 0 and 2.

2. When PC reaches the end of segment FF:, it loops to the reset address FF:0000h (for compatibility with the C51 Architecture). When PC

increments beyond the end of segment FE:, it continues at the reset address FF:0000h (linearity). When PC increments beyond the end of

segment 01:, it loops to the beginning of segment 00: (this prevents from its going into the reserved area).

On-chip ROM/EPROM

Code Memory

Program/code

Segments

Program/code

External Memory Space

32 Kbytes

EA#= 0

EA#= 1

32 Kbytes

32 Kbytes

Reserved

64 Kbytes

128 Kbytes

FF:FFFFh

FF:8000h

FF:7FFFh

FF:0000h

FE:FFFFh

FE:0000h

FD:FFFFh

01:FFFFh

01:0000h

00:FFFFh

02:0000h

00:0000h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC251G2DXXX-24IA | IC CYCLONE III FPGA 80K 484 FBGA |

| TSC251G2DXXX-24IB | IC CYCLONE III FPGA 80K 780FBGA |

| TSC251G2DXXX-L16CB | IC CYCLONE III FPGA 80K 780FBGA |

| TSC251G2DXXX-L16CED | IC CYCLONE III FPGA 80K 780FBGA |

| TSC87251G2D-24CED | Process/Temperature Controller; Control Operation:Auto/Manual, Ramp/Soak, Stand By, Valve Positioning; Control Output Relay Rating:264 VAC / 2 A; Control Type:On/Off, PID; Controller Output Type 1:Relay RoHS Compliant: NA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSC251G2DXXX-24IA | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8/16-bit Microcontroller with Serial Communication Interfaces |

| TSC251G2DXXX-24IB | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8/16-bit Microcontroller with Serial Communication Interfaces |

| TSC251G2DXXX-L16CB | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8/16-bit Microcontroller with Serial Communication Interfaces |

| TSC251G2DXXX-L16CE | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:8/16-bit Microcontroller with Serial Communication Interfaces |

| TSC251G2DXXX-L16CED | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。