- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382686 > TSB41AB3 IC APEX 20KE FPGA 400K 672-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | TSB41AB3 |

| 英文描述: | IC APEX 20KE FPGA 400K 672-FBGA |

| 中文描述: | 3個(gè)IEEE 1394a端口電纜收發(fā)器/仲裁器 |

| 文件頁數(shù): | 7/50頁 |

| 文件大?。?/td> | 662K |

| 代理商: | TSB41AB3 |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

SLLS418G

–

JUNE 2000

–

REVISED JANUARY 2003

7

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

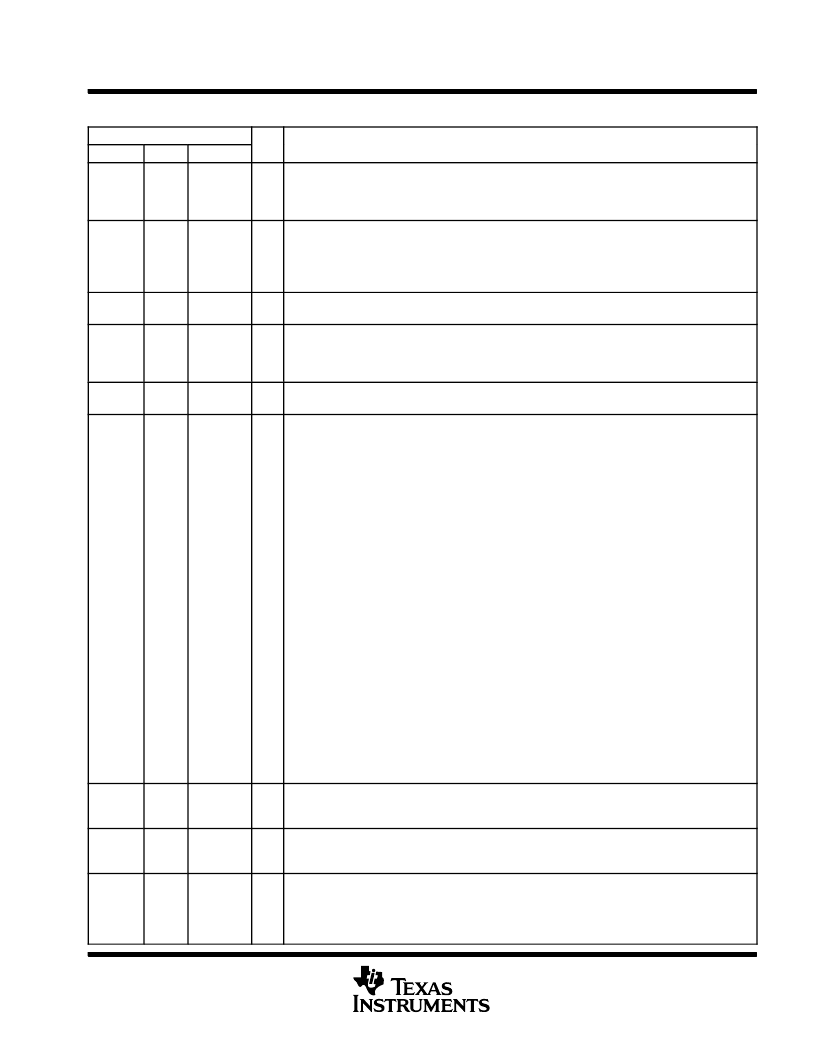

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

AGND

TYPE

Supply

NO.

36, 37, 38,

39, 40, 41,

60, 61, 64,

65

–

Analog circuit ground terminals. These terminals must be tied together to the low-impedance circuit

board ground plane.

AVDD

Supply

34, 35, 47,

48, 54, 62,

63

–

Analog circuit power terminals. A combination of high-frequency decoupling capacitors near each

terminal are suggested, such as paralleled 0.1

μ

F and 0.001

μ

F. Lower frequency 10-

μ

F filtering

capacitors are also recommended. These supply terminals are separated from PLLVDD and DVDD

internal to the device to provide noise isolation. They must be tied at a low-impedance point on the

circuit board.

CNA

CMOS

17

O

Cable not active output. This terminal is asserted high when there are no ports receiving incoming bias

voltage.

CPS

CMOS

27

I

Cable power status input. This terminal is normally connected to cable power through a 400-k

resistor. This circuit drives an internal comparator that is used to detect the presence of cable power.

This terminal must be tied to DVDD supply through a 1-k

resistor if application does not require it to be

used.

CTL0

CTL1

CMOS

5 V tol

4

5

I/O

Control I/Os. These bidirectional signals control communication between the TSB41AB3 and the LLC.

Bus holders are built into these terminals.

C/LKON

CMOS

22

I/O

Bus manager contender programming input and link-on output. On hardware reset, this terminal is

used to set the default value of the contender status indicated during self-ID. Programming is done by

tying the terminal through a 10-k

resistor to a high (contender) or low (not contender). The resistor

allows the link-on output to override the input. However, it is recommended that this terminal be

programmed low, and that the contender status be set via the C register bit.

If the TSB41AB3 is used with an LLC that has a dedicated terminal for monitoring LKON and also

setting the contender status, then a 10-k

series resistor is placed on the LKON line between the PHY

and LLC to prevent bus contention.

Following hardware reset, this terminal is the link-on output, which is used to notify the LLC to

power-up and become active. The link-on output is a square-wave signal with a period of

approximately 163 ns (8 SYSCLK cycles) when active. The link-on output is otherwise driven low,

except during hardware reset when it is high impedance.

The link-on output is activated if the LLC is inactive (LPS inactive or the LCtrl bit cleared) and when one

of the following is true:

a) the PHY receives a link-on PHY packet addressed to this node

b) the PEI (port-event interrupt) register bit is 1

c) any of the CTOI (configuration-timeout interrupt), CPSI (cable-power-status interrupt), or STOI

(state-timeout interrupt) register bits are 1 and the RPIE (resuming-port interrupt enable) register

bit is also 1.

Once activated, the link-on output stays active until the LLC becomes active (both LPS active and the

LCtrl bit set). The PHY also deasserts the link-on output when a bus-reset occurs unless the link-on

output is otherwise active because one of the interrupt bits is set (i.e., the link-on output is active due

solely to the reception of a link-on PHY packet).

NOTE: If an interrupt condition exists which otherwise causes the link-on output to be activated if the

LLC were inactive, the link-on output is activated when the LLC subsequently becomes inactive.

DGND

Supply

3, 16, 20,

21, 28, 70,

80

–

Digital circuit ground terminals. These terminals must be tied together to a low-impedance point on the

circuit board ground plane.

D0

–

D7

CMOS

5 V tol

7, 8, 10,

11, 12, 13,

14, 15

I/O

Data I/Os. These are bidirectional data signals between the TSB41AB3 and the LLC. Bus holders are

built into these terminals.

DVDD

Supply

6, 29, 30,

68, 69, 79

–

Digital circuit power terminals. A combination of high-frequency decoupling capacitors near each

terminal is suggested, such as paralleled 0.1

μ

F and 0.001

μ

F. Lower frequency 10-

μ

F filtering

capacitors are also recommended. These supply terminals are separated from PLLVDD and AVDD

internal to the device to provide noise isolation. They must be tied at a low-impedance point on the

circuit board.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSB41BA3-EP | IC APEX 20KE FPGA 400K 672-FBGA |

| TSB41LV03PFP | IC APEX 20KE FPGA 600K 652-BGA |

| TSB41AB2I | IEEE 1394a-2000 TWO-PORT CABLE TRANSCEVER/ARBITER |

| TSB41LV03AI | IEEE 1394a THREE-PORT CABLE TRANSCEIVER/ARBITER |

| TSC692E | 672-pin FineLine BGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSB41AB3-EP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:IEEE 1394A-2000 THREE-PORT CABLE TRANSCEIVER/ARBITER |

| TSB41AB3IPFP | 功能描述:緩沖器和線路驅(qū)動(dòng)器 Three-Port Cable Xcvr/Arbiter RoHS:否 制造商:Micrel 輸入線路數(shù)量:1 輸出線路數(shù)量:2 極性:Non-Inverting 電源電壓-最大:+/- 5.5 V 電源電壓-最小:+/- 2.37 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:MSOP-8 封裝:Reel |

| TSB41AB3IPFP | 制造商:Texas Instruments 功能描述:IC TRX/ARBITER 1394A 3 PORT 80HTQFP |

| TSB41AB3IPFPEP | 功能描述:1394 接口集成電路 Mil Enh 3-Port Cable Xcvr/Arbiter RoHS:否 制造商:Texas Instruments 類型:Link Layer Controller 工作電源電壓: 封裝 / 箱體:LQFP 封裝:Tray |

| TSB41AB3IPFPG4 | 制造商:Texas Instruments 功能描述:THREE PORT CBL TRNSCVR/ARBITER 1TX 1RX 400MBPS 80HTQFP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。