- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383960 > TMX320C6411AZLZ (Texas Instruments, Inc.) FIXED POINT DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMX320C6411AZLZ |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 定點(diǎn)數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 41/119頁(yè) |

| 文件大小: | 1742K |

| 代理商: | TMX320C6411AZLZ |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)當(dāng)前第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)

SPRS196H MARCH 2002 REVISED JULY 2004

41

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

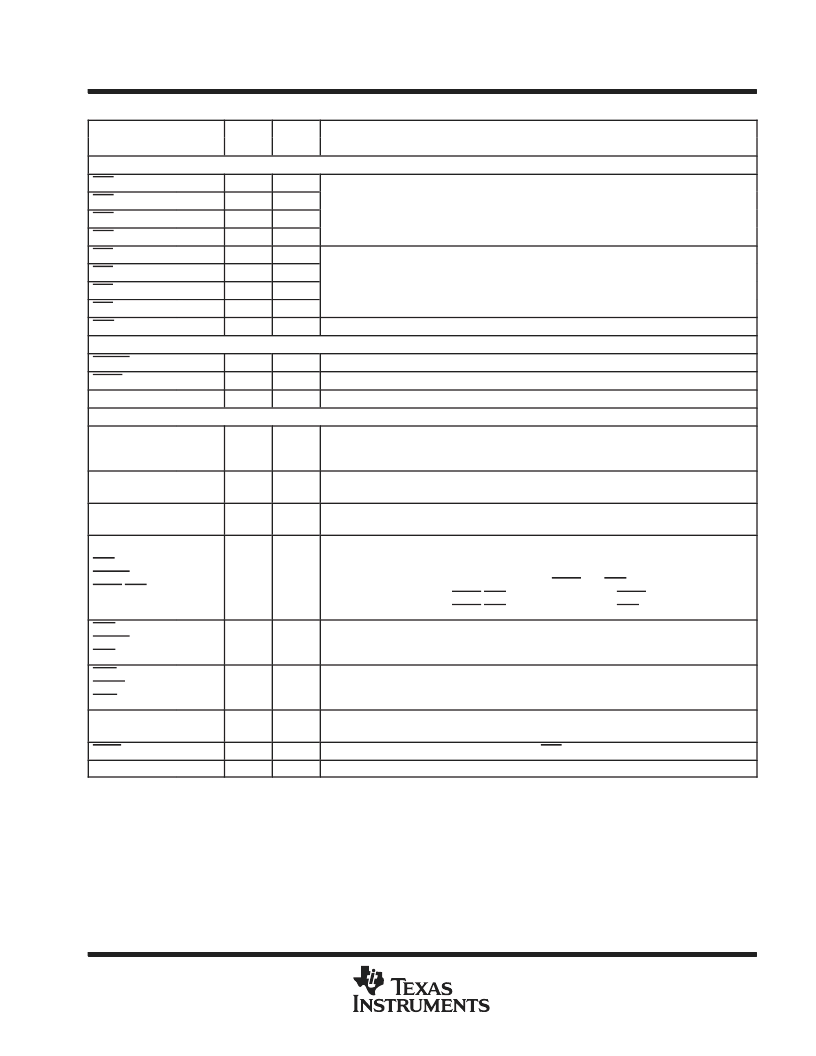

Terminal Functions (Continued)

SIGNAL

TYPE

IPD/

IPU

DESCRIPTION

NAME

NO.

EMIF (32-bit) CONTROL SIGNALS COMMON TO ALL TYPES OF MEMORY§

O/Z

IPU

EMIF memory space enables

O/Z

IPU

O/Z

IPU

CE3

L26

CE2

K23

O/Z

IPU

CE1

K24

Enabled by bits 28 through 31 of the word address

Only one pin is asserted during any external data access

CE0

K25

BE3

M25

O/Z

IPU

EMIF byte-enable control

Decoded from the low-order address bits. The number of address bits or byte enables

used depends on the width of external memory.

Byte-write enables for most types of memory

Can be directly connected to SDRAM read and write mask signal (SDQM)

EMIF peripheral data transfer, allows direct transfer between external peripherals

EMIF (32-BIT) BUS ARBITRATION§

BE2

M26

O/Z

IPU

BE1

L23

O/Z

IPU

BE0

L24

O/Z

IPU

PDT

M22

O/Z

IPU

HOLDA

N22

O

IPU

EMIF hold-request-acknowledge to the host

HOLD

V23

I

IPU

EMIF hold request from the host

BUSREQ

P22

O

IPU

EMIF bus request output

EMIF (32-BIT) ASYNCHRONOUS/SYNCHRONOUS MEMORY CONTROL§

ECLKIN

H25

I

IPD

EMIF external input clock. The EMIF input clock (ECLKIN, CPU/4 clock, or CPU/6 clock) is

selected at reset via the pullup/pulldown resistors on the ECLKIN_SEL[1:0] pins.

AECLKIN is the default for the EMIF input clock.

ECLKOUT2

J23

O/Z

IPD

EMIF output clock 2. Programmable to be EMIF input clock (ECLKIN, CPU/4 clock, or CPU/6

clock) frequency divided-by-1, -2, or -4.

ECLKOUT1

J26

O/Z

IPD

EMIF output clock 1 at EMIF input clock (ECLKIN, CPU/4 clock, or CPU/6 clock)

frequency.

ARE/

SDCAS/

SADS/SRE

J25

O/Z

IPU

EMIF asynchronous memory read-enable/SDRAM column-address strobe/programmable

synchronous interface-address strobe or read-enable

For programmable synchronous interface, the RENEN field in the CE Space Secondary

Control Register (CExSEC) selects between SADS and SRE:

If RENEN = 0, then the SADS/SRE signal functions as the SADS signal.

If RENEN = 1, then the SADS/SRE signal functions as the SRE signal.

AOE/

SDRAS/

SOE

J24

O/Z

IPU

EMIF asynchronous memory output-enable/SDRAM row-address strobe/programmable

synchronous interface output-enable

AWE/

SDWE/

SWE

K26

O/Z

IPU

EMIF asynchronous memory write-enable/SDRAM write-enable/programmable

synchronous interface write-enable

SDCKE

L25

O/Z

IPU

EMIF SDRAM clock-enable (used for self-refresh mode).

If SDRAM is not in system, SDCKE can be used as a general-purpose output.

SOE3

R22

O/Z

IPU

EMIF synchronous memory output-enable for CE3 (for glueless FIFO interface)

ARDY

I = Input, O = Output, Z = High impedance, S = Supply voltage, GND = Ground

IPD = Internal pulldown, IPU = Internal pullup. (These IPD/IPU signal pins feature a 30-k

IPD or IPU resistor. To pull up a signal to the opposite

supply rail, a 1-k

resistor should be used, unless otherwise noted.)

§To maintain signal integrity for the EMIF signals, serial termination resistors should be inserted into all EMIF output signal lines.

L22

I

IPU

Asynchronous memory ready input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMX320C6411GLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMX320C6411ZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMX32C6411AGLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP32C6411AZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

| TMP320C6411AZLZ | FIXED POINT DIGITAL SIGNAL PROCESSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMX320C6411GLZ | 制造商:Rochester Electronics LLC 功能描述:C6411 1V/300MHZ PROTOTYPES - Bulk 制造商:Texas Instruments 功能描述: |

| TMX320C6411GLZ300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZ5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZA300 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6411GLZA5E0 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。