- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98255 > TLV320DAC32IRHBTG4 (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 PDF資料下載

參數(shù)資料

| 型號: | TLV320DAC32IRHBTG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| 封裝: | 5 X 5 MM, GREEN, PLASTIC, QFN-32 |

| 文件頁數(shù): | 56/69頁 |

| 文件大小: | 1242K |

| 代理商: | TLV320DAC32IRHBTG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁當(dāng)前第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁

SLAS506B – NOVEMBER 2006 – REVISED DECEMBER 2008........................................................................................................................................ www.ti.com

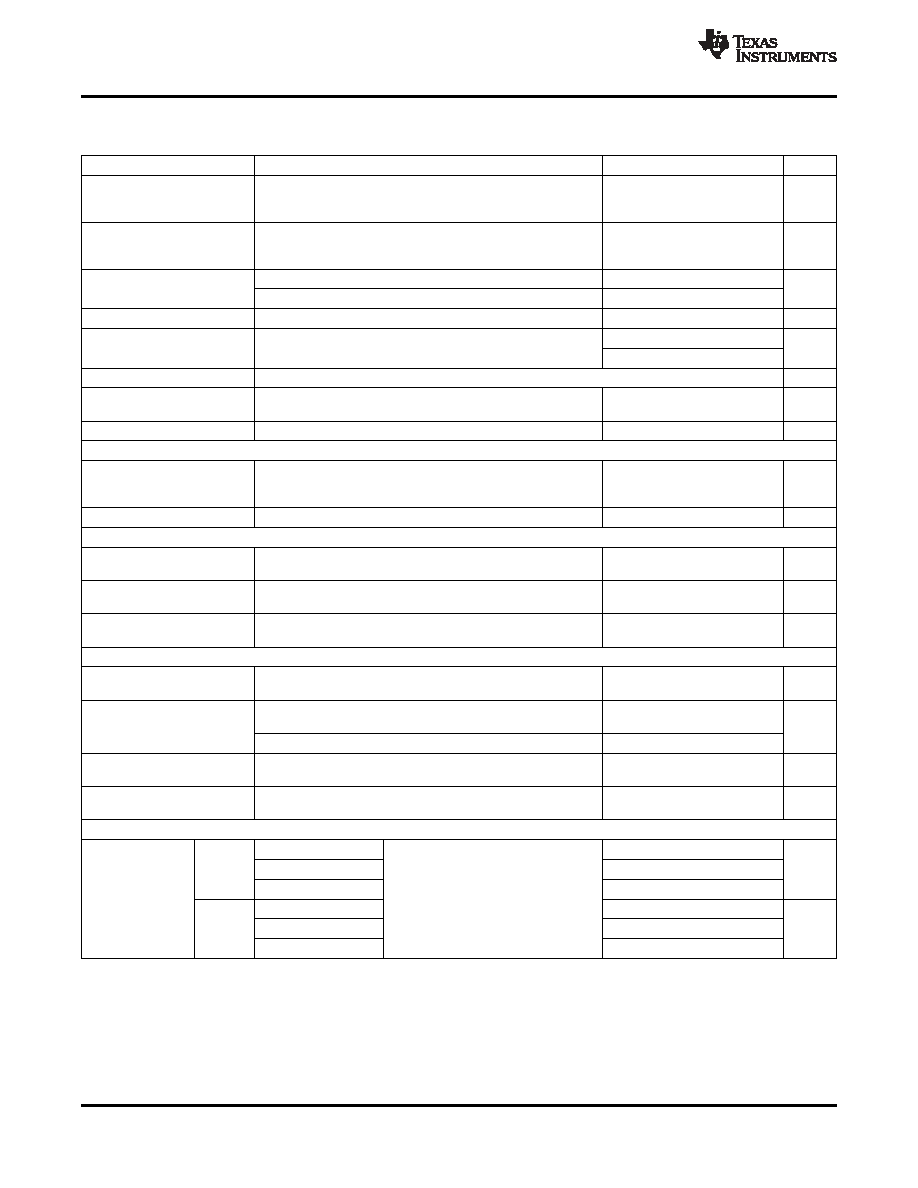

ELECTRICAL CHARACTERISTICS (continued)

At 25C, AVDD_DAC, DRVDD, IOVDD = 3.3 V, DVDD = 1.8 V, Fs = 48 kHz, 16-bit audio data (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Maximum

programmable output

9

dB

level control gain

Programmable output

level control gain step

1

dB

size

RL = 32 , 0.1% THD

25

PO

Maximum output power

mW

RL = 16 , 0.1% THD

50

SNR

Signal-to-noise ratio(2)

85

94

dB

–79

–60

Total harmonic

1-kHz Output, PO = 26 mW, RL = 16

dB%

distortion

0.011

Channel separation

1 kHz, 0-dB Input

85

dB

Power supply rejection

1 KHz, 100 mVpp on AVDD_DAC, DRVDD1/2

52

dB

ratio

Mute attenuation

1-kHz Output

107

dB

DIFFERENTIAL STEREO HEADPHONE DRIVER

0-dB Gain to high power outputs. Output

0-dB full-scale output

common-mode voltage setting = 1.65 V,

1.27

V

voltage

Differential output configuration(3)

SNR

Signal-to-noise ratio(4)

95

dB

DIFFERENTIAL SPEAKER DRIVER

DRVDD = 3.6 V, HPLCOM = 1.8 V,

PO

Maximum output power

0.5

W

HPLCOM/HPRCOM Gain = 5, RL = 8

0-dB Full-scale output

0-dB Gain for HPLCOM/HPRCOM,

1.15

Vrms

voltage

Output common-mode voltage setting = 1.65 V, RL = 8

Total harmonic

Fs = 48 kHz, 0-dB Full-scale signal,

–71

dB

distortion

0-dB Gain at HPLCOM/HPRCOM, RL = 8

DIGITAL I/O

0.3

VIL

Input low level

IIL = +5 A

–0.3

V

IOVDD

0.7

IIH = +5 A, IOVDD > 1.6 V

IOVDD

VIH

Input high level(5)

V

IIH = +5 A, IOVDD < 1.6 V

IOVDD

0.1

VOL

Output low level

IIH = 2 TTL loads

V

IOVDD

0.8

VOH

Output high level

IOH = 2 TTL loads

V

IOVDD

SUPPLY CURRENT

AVDD_DAC+DRVDD

3.99

Current

DVDD

0.025

mA

LINEL/R only routed to single-ended

stereo headphones, DAC = off, Analog

IOVDD

0.001

Headphone

Mixer = on, PLL = off, LDO = off,

amplifier

AVDD_DAC+DRVDD

13.17

analog mixer enabled, no signal

applied

Power

DVDD

0.045

mW

IOVDD

0.003

(2)

Ratio of output level with a 1-kHz full-scale input, to the output level playing an all-zero signal, measured , A-weighted over a 20-Hz to

20-kHz bandwidth.

(3)

Unless otherwise noted, all measurements use output common-mode voltage setting of 1.35 V, 0-dB output level control gain, 16-

differential load.

(4)

Ratio of output level with a 1-kHz full-scale input, to the output level playing an all-zero signal, measured , A-weighted over a 20-Hz to

20-kHz bandwidth.

(5)

When IOVDD < 1.6 V, minimum VIH is 1.1 V.

6

Copyright 2006–2008, Texas Instruments Incorporated

Product Folder Link(s): TLV320DAC32

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320DAC32IRHBT | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| TLV320DAC32IRHBRG4 | SERIAL INPUT LOADING, DAC WITH PROGRAMMABLE PLL, PQCC32 |

| TLV431AIDBV | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, 1.24 V, PDSO5 |

| TLV431ALPRE | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

| TLV431ALP | 1-OUTPUT TWO TERM VOLTAGE REFERENCE, PBCY3 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320DAC33NIZQC | 制造商:Texas Instruments 功能描述: |

| TLV320DAC33NIZQCR | 制造商:Texas Instruments 功能描述: |

| TLV320VD30 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:VDSL CODEC |

| TLV320VD30PN | 制造商:Texas Instruments 功能描述: |

| TLV321AC36 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V VOICE-BAND AUDIO PROCESSORS (VBAPE) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。