- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄383992 > TE28F020-120 (INTEL CORP) 28F020 2048K (256K X 8) CMOS FLASH MEMORY PDF資料下載

參數(shù)資料

| 型號: | TE28F020-120 |

| 廠商: | INTEL CORP |

| 元件分類: | DRAM |

| 英文描述: | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| 中文描述: | 256K X 8 FLASH 12V PROM, 120 ns, PDSO32 |

| 封裝: | 0.310 X 0.720 INCH, TSOP-32 |

| 文件頁數(shù): | 8/38頁 |

| 文件大小: | 878K |

| 代理商: | TE28F020-120 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁

28F020

E

8

28F020

28F020

A

0

-A

17

DQ

0

-DQ

7

CE

#

WE

#

OE

#

A

0

-A

17

DQ

0

-DQ

7

CE

#

BHE

#

OE

#

V

CC

V

CC

V

PP

V

PP

80C186

System Bus

A

1

-A

18

DQ

8

-DQ

15

Address Decoded

Chip Select

DQ

0

-DQ

7

WE

#

WR

#

RD

#

V

CC

V

CC

A

0

0245_03

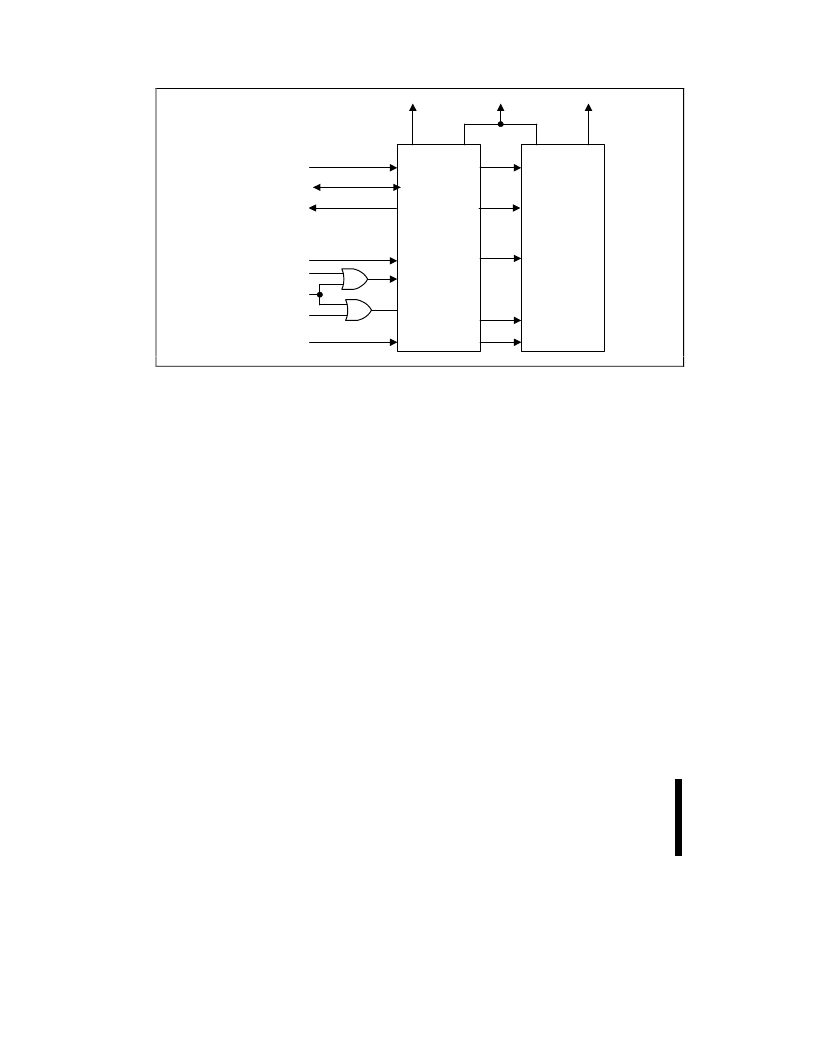

Figure 3. 28F020 in an 80C186 System

2.0 PRINCIPLES OF OPERATION

Flash memory augments EPROM functionality with

in-circuit electrical erasure and reprogramming.

The 28F020 introduces a command register to

manage this new functionality. The command

register allows for 100% TTL-level control inputs,

fixed

power

supplies

programming, and maximum EPROM compatibility.

during

erasure

and

In the absence of high voltage on the V

PP

pin, the

28F020 is a read-only memory. Manipulation of the

external memory control pins yields the standard

EPROM read, standby, output disable, and

intelligent identifier operations.

The same EPROM read, standby, and output

disable operations are available when high voltage

is applied to the V

PP

pin. In addition, high voltage

on V

PP

enables erasure and programming of the

device. All functions associated with altering

memory contents

—intelligent identifier, erase,

erase verify, program, and program verify—are

accessed via the command register.

Commands are written to the register using

standard microprocessor write timings. Register

contents serve as input to an internal state

machine

which

controls

programming circuitry. Write cycles also internally

latch addresses and data needed for programming

or

erase

operations.

command written to the register, standard

microprocessor read timings output array data,

access the intelligent identifier codes, or output

data for erase and program verification.

the

erase

and

With

the

appropriate

2.1

Integrated Stop Timer

Successive command write cycles define the

durations of program and erase operations;

specifically, the program or erase time durations

are normally terminated by associated Program or

Erase Verify commands. An integrated stop timer

provides simplified timing control over these

operations; thus eliminating the need for maximum

program/erase timing specifications. Programming

and erase pulse durations are minimums only.

When the stop timer terminates a program or erase

operation, the device enters an inactive state and

remains inactive until receiving the appropriate

Verify or Reset command.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TE28F020-150 | 28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| TE28F128P30T85 | Intel StrataFlash Embedded Memory |

| TE28F128P30xxx | Intel StrataFlash Embedded Memory |

| TE28F256P30B85 | Intel StrataFlash Embedded Memory |

| TE28F256P30T85 | Intel StrataFlash Embedded Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TE28F020-150 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| TE28F020-90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:28F020 2048K (256K X 8) CMOS FLASH MEMORY |

| TE28F032B3B110 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| TE28F032B3B90 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

| TE28F032B3BA110 | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:SMART 3 ADVANCED BOOT BLOCK 4-, 8-, 16-, 32-MBIT FLASH MEMORY FAMILY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。