- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄25648 > ST72P63BH4T1 (STMICROELECTRONICS) 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | ST72P63BH4T1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 8 MHz, MICROCONTROLLER, PQFP48 |

| 封裝: | 7 X 7 MM, ROHS COMPLIANT, LQFP-48 |

| 文件頁數(shù): | 145/145頁 |

| 文件大小: | 2984K |

| 代理商: | ST72P63BH4T1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁當前第145頁

ST7263BDx ST7263BHx ST7263BKx ST7263BE

99/145

8-bit A/D converter (ADC) (Cont’d)

12.6.3.2 Digital A/D conversion result

The conversion is monotonic, meaning that the re-

sult never decreases if the analog input does not

and never increases if the analog input does not.

If the input voltage (VAIN) is greater than or equal

to VDDA (high-level voltage reference) then the

conversion result in the DR register is FFh (full

scale) without overflow indication.

If input voltage (VAIN) is lower than or equal to

VSSA (low-level voltage reference) then the con-

version result in the DR register is 00h.

The A/D converter is linear and the digital result of

the conversion is stored in the ADCDR register.

The accuracy of the conversion is described in the

parametric section.

RAIN is the maximum recommended impedance

for an analog input signal. If the impedance is too

high, this will result in a loss of accuracy due to

leakage and sampling not being completed in the

alloted time.

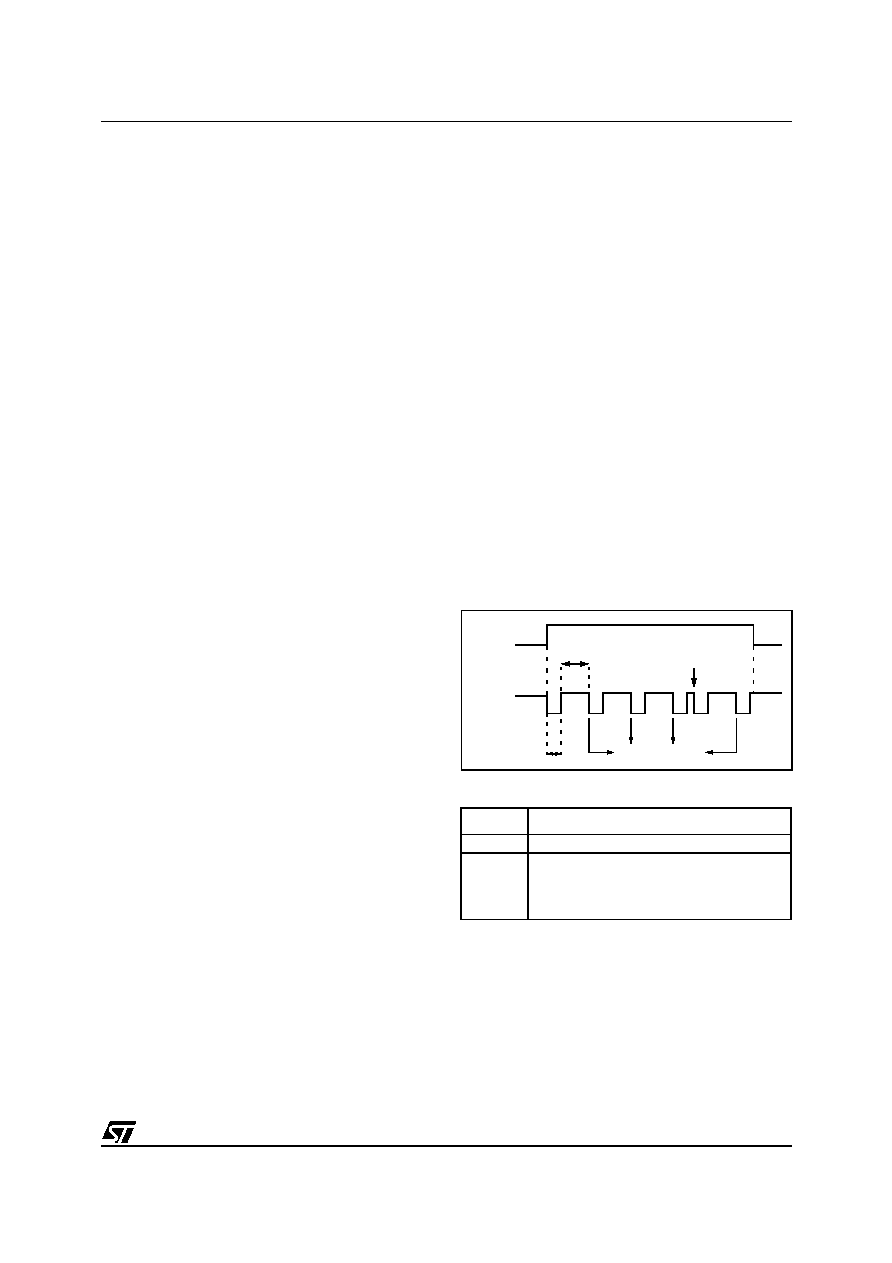

12.6.3.3 A/D conversion phases

The A/D conversion is based on two conversion

phases as shown in Figure 48:

■

Sample capacitor loading [duration: tLOAD]

During this phase, the VAIN input voltage to be

measured is loaded into the CADC sample

capacitor.

■

A/D conversion [duration: tCONV]

During this phase, the A/D conversion is

computed (8 successive approximations cycles)

and the CADC sample capacitor is disconnected

from the analog input pin to get the optimum

analog to digital conversion accuracy.

While the ADC is on, these two phases are contin-

uously repeated.

At the end of each conversion, the sample capaci-

tor is kept loaded with the previous measurement

load. The advantage of this behaviour is that it

minimizes the current consumption on the analog

pin in case of single input channel measurement.

12.6.3.4 Software Procedure

Refer to the control/status register (CSR) and data

register (DR) in Section 12.6.6 for the bit defini-

tions and to Figure 48 for the timings.

ADC configuration

The total duration of the A/D conversion is 12 ADC

clock periods (1/fADC=4/fCPU).

The analog input ports must be configured as in-

put, no pull-up, no interrupt. Refer to the I/O

ports chapter. Using these pins as analog inputs

does not affect the ability of the port to be read as

a logic input.

In the CSR register:

– Select the CH[3:0] bits to assign the analog

channel to be converted.

ADC conversion

In the CSR register:

– Set the ADON bit to enable the A/D converter

and to start the first conversion. From this time

on, the ADC performs a continuous conver-

sion of the selected channel.

When a conversion is complete

– The COCO bit is set by hardware.

– No interrupt is generated.

– The result is in the DR register and remains

valid until the next conversion has ended.

A write to the CSR register (with ADON set) aborts

the current conversion, resets the COCO bit and

starts a new conversion.

Figure 48. ADC conversion timings

12.6.4 Low power modes

Note: The A/D converter may be disabled by reset-

ting the ADON bit. This feature allows reduced

power consumption when no conversion is needed

and between single shot conversions.

12.6.5 Interrupts

None

Mode

Description

Wait

No effect on A/D Converter

Halt

A/D Converter disabled.

After wakeup from Halt mode, the A/D Con-

verter requires a stabilisation time before ac-

curate conversions can be performed.

ADCCSR WRITE

ADON

COCO BIT SET

tLOAD

tCONV

OPERATION

HOLD

CONTROL

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| STF-H240IYD | T-1 DUAL COLOR LED ARRAY, RED/YELLOW, 3 mm |

| STM32F103CBT6 | 32-BIT, FLASH, 72 MHz, RISC MICROCONTROLLER, PQFP48 |

| STM32F103R8T7TR | 32-BIT, FLASH, 1.25 MHz, RISC MICROCONTROLLER, PQFP64 |

| STM32W108HBU7 | SPECIALTY MICROPROCESSOR CIRCUIT, QCC40 |

| STP506C-2IW-012V | SINGLE COLOR DISPLAY CLUSTER, WHITE, 152.4 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST72T101G1B6 | 功能描述:8位微控制器 -MCU OTP EPROM 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72T101G1M6 | 功能描述:8位微控制器 -MCU OTP EPROM 4K SPI RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72T101G2B6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72T101G2M6 | 功能描述:8位微控制器 -MCU RO 511-ST72C104G2M6 RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72T121J2B6 | 功能描述:8位微控制器 -MCU OTP EPROM 8K SPI/SCI RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。