- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄368020 > PI7C8150 PCI Bridge | 2-Port PCI-to-PCI Bridge PDF資料下載

參數(shù)資料

| 型號(hào): | PI7C8150 |

| 英文描述: | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| 中文描述: | PCI橋| 2端口PCI至PCI橋 |

| 文件頁(yè)數(shù): | 106/115頁(yè) |

| 文件大小: | 879K |

| 代理商: | PI7C8150 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)當(dāng)前第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)

PI7C8150B

2-PORT PCI-TO-PCI BRIDGE

ADVANCE INFORMATION

Page 106 of 115

July 31, 2003 – Revision 1.031

TCK. The value of the test mode state (TMS) input signal at a rising edge of TCK controls

the sequence of state changes. The TAP controller is initialized after power-up by applying

a low to the TRST_L pin. In addition, the TAP controller can be initialized by applying a

high signal level on the TMS input for a minimum of five TCK periods.

For greater detail on the behavior of the TAP controller, test logic in each controller state

and the state machine and public instructions, refer to the IEEE 1149.1 Standard Test

Access Port and Boundary-Scan Architecture document (available from the IEEE).

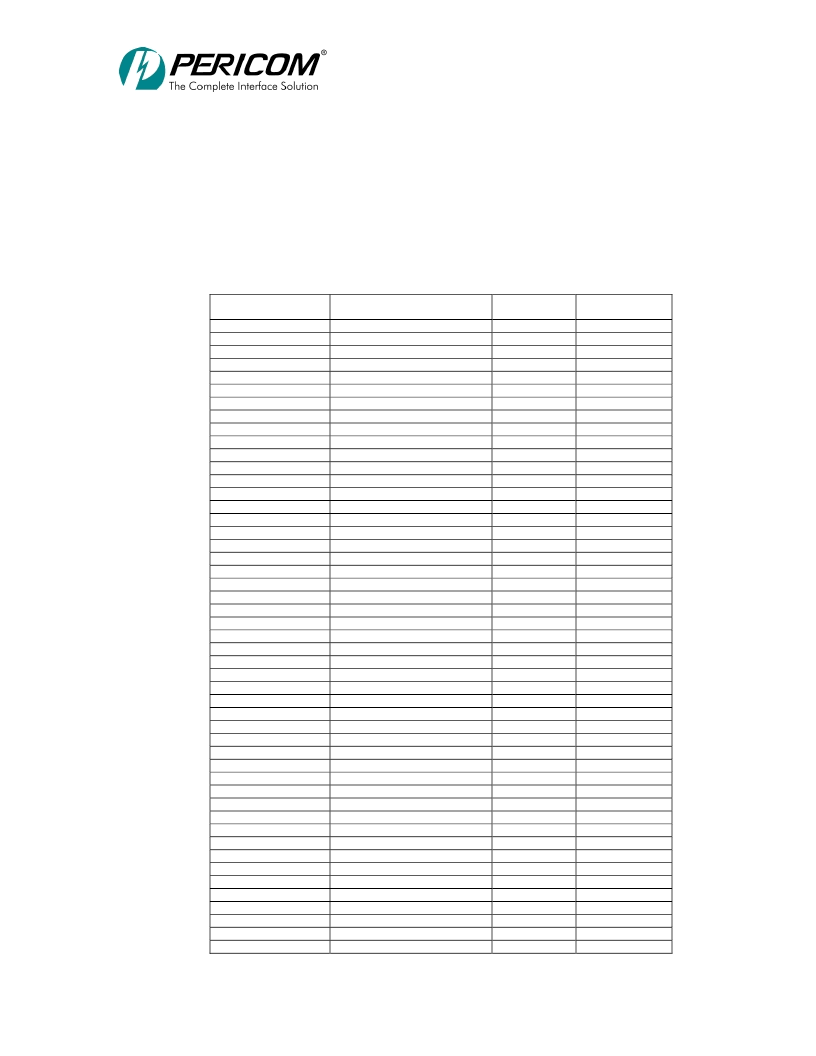

Table 16-2. JTAG Boundary Register Order

Boundary-Scan

Register Number

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

Pin Name

Pin Number

Type

S_AD[0]

S_AD[1]

S_AD[2]

S_AD[3]

S_AD[4]

S_AD[5]

S_AD[6]

S_AD[7]

S_CBE[0]

S_AD[8]

S_AD[9]

S_M66EN

S_AD[10]

S_AD[11]

S_AD[12]

S_AD[13]

S_AD[14]

S_AD[15]

S_CBE[1]

S_PAR

S_SERR_L

S_PERR_L

S_LOCK_L

S_STOP_L

S_DEVSEL_L

S_TRDY_L

S_IRDY_L

S_FRAME_L

S_CBE[2]

S_AD[16]

S_AD[17]

S_AD[18]

S_AD[19]

S_AD[20]

S_AD[21]

S_AD[22]

S_AD[23]

S_CBE[3]

S_AD[24]

S_AD[25]

S_AD[26]

S_AD[27]

S_AD[28]

S_AD[29]

S_AD[30]

S_AD[31]

137

138

140

141

143

144

146

147

149

150

152

153

154

159

161

162

164

165

167

168

169

171

172

173

175

176

177

179

180

182

183

185

186

188

189

191

192

194

195

197

198

200

201

203

204

206

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

OUTPUT

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

CONTROL

BIDIR

BIDIR

INPUT

BIDIR

BIDIR

BIDIR

CONTROL

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

BIDIR

CONTROL

BIDIR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PI7C8150-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A-33 | PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150B | PCI Bridge | Asynchronous 2-Port PCI Bridge |

| PI7C8152A | ENHANCED 2- PORT TO PCI BRIDGE INTEL 21152 COMPORISON |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PI7C8150-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150A-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:PCI Bridge | 2-Port PCI-to-PCI Bridge |

| PI7C8150AMA | 制造商:Pericom Semiconductor Corporation 功能描述:PCI to PCI Bridge 208-Pin FQFP |

| PI7C8150AMA-33 | 制造商:Pericom Semiconductor Corporation 功能描述:PCI-to-PCI Bridge 208-Pin FQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。