- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16874 > PCM18XT0 (Microchip Technology)MODULE PROC PIC18F4685 PDF資料下載

參數(shù)資料

| 型號(hào): | PCM18XT0 |

| 廠商: | Microchip Technology |

| 文件頁數(shù): | 177/183頁 |

| 文件大小: | 0K |

| 描述: | MODULE PROC PIC18F4685 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 附件類型: | 處理器模塊 |

| 適用于相關(guān)產(chǎn)品: | ICE2000 |

| 產(chǎn)品目錄頁面: | 658 (CN2011-ZH PDF) |

| 配用: | ICE2000-ND - EMULATOR MPLAB-ICE 2000 POD |

| 相關(guān)產(chǎn)品: | DVA18XP400-ND - DEVICE ADAPTER 18F4220 PDIP 40LD DVA18XP280-ND - DEVICE ADAPTER 18F2220 PDIP 28LD DVA18PQ440-ND - DEVICE ADAPTER 18F4220 TQFP 44LD |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁當(dāng)前第177頁第178頁第179頁第180頁第181頁第182頁第183頁

2011 Microchip Technology Inc.

DS39931D-page 93

PIC18F46J50 FAMILY

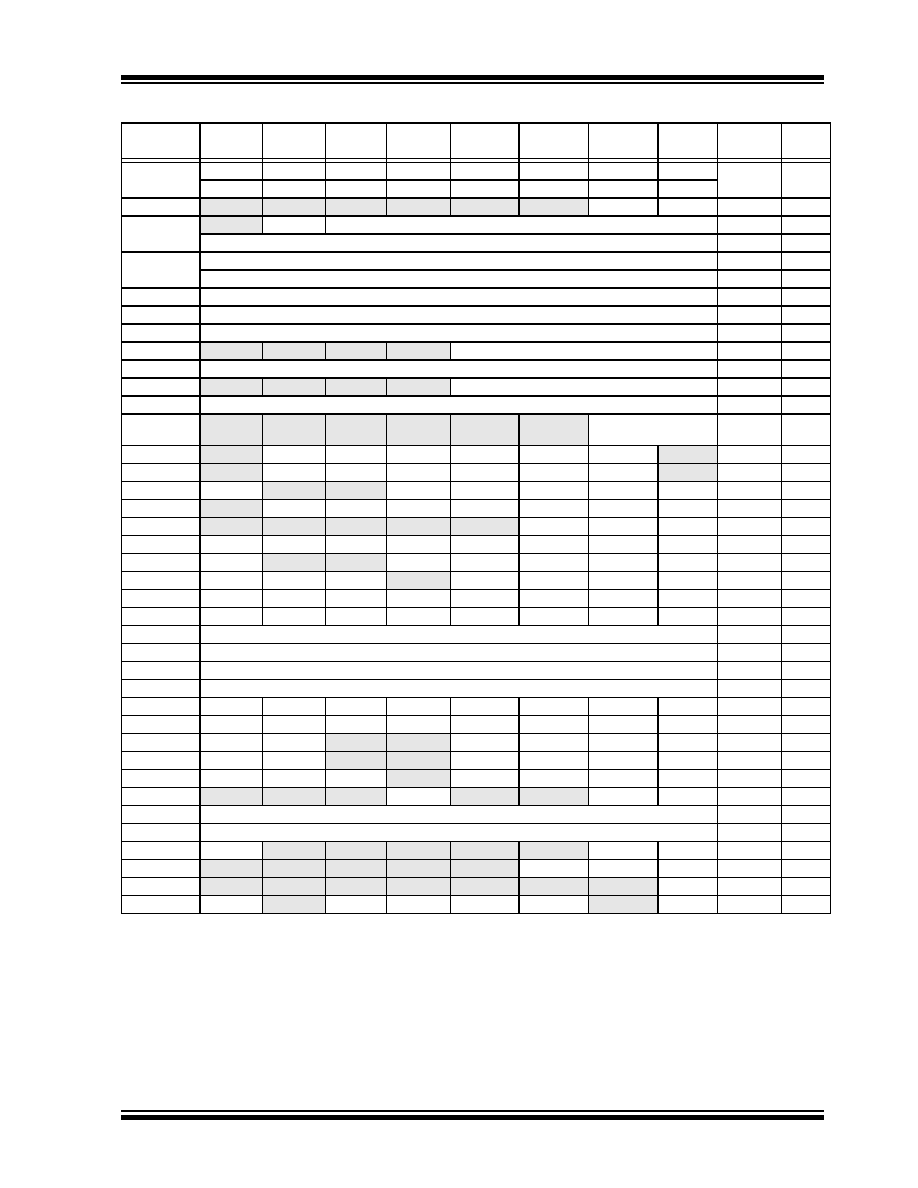

SSP2CON2

GCEN

ACKSTAT

ACKDT

ACKEN

RCEN

PEN

RSEN

SEN

0000 0000

GCEN

ACKSTAT

ADMSK3(4)

ADMSK2(4)

ADMSK1(4)

SEN

CMSTAT

—

COUT2

COUT1

---- --11

PMADDRH/

—

CS1

Parallel Master Port Address High Byte

-000 0000

PMDOUT1H(5,6) Parallel Port Out Data High Byte (Buffer 1)

0000 0000

PMADDRL/

Parallel Master Port Address Low Byte

0000 0000

PMDOUT1L(5,6) Parallel Port Out Data Low Byte (Buffer 0)

0000 0000

PMDIN1H(5)

Parallel Port In Data High Byte (Buffer 1)

0000 0000

PMDIN1L(5)

Parallel Port In Data Low Byte (Buffer 0)

0000 0000

TXADDRL

SPI DMA Transit Data Pointer Low Byte

xxxx xxxx

TXADDRH

—

SPI DMA Transit Data Pointer High Byte

---- xxxx

RXADDRL

SPI DMA Receive Data Pointer Low Byte

xxxx xxxx

RXADDRH

—

SPI DMA Receive Data Pointer High Byte

---- xxxx

DMABCL

SPI DMA Byte Count Low Byte

xxxx xxxx

DMABCH

—

SPI DMA Byte Count High

Byte

---- --xx

UCON

—

PPBRST

SE0

PKTDIS

USBEN

RESUME

SUSPND

—

-0x0 000-

USTAT

—

ENDP3

ENDP2

ENDP1

ENDP0

DIR

PPBI

—

-xxx xxx-

UEIR

BTSEF

—

BTOEF

DFN8EF

CRC16EF

CRC5EF

PIDEF

0--0 0000

UIR

—

SOFIF

STALLIF

IDLEIF

TRNIF

ACTVIF

UERRIF

URSTIF

-000 0000

UFRMH

—

—FRM10

FRM9

FRM8

---- -xxx

UFRML

FRM7

FRM6

FRM5

FRM4

FRM3

FRM2

FRM1

FRM0

xxxx xxxx

PMCONH(5)

PMPEN

—

ADRMUX1

ADRMUX0

PTBEEN

PTWREN

PTRDEN

0--0 0000

PMCONL(5)

CSF1

CSF0

ALP

—

CS1P

BEP

WRSP

RDSP

000- 0000

PMMODEH(5)

BUSY

IRQM1

IRQM0

INCM1

INCM0

MODE16

MODE1

MODE0

0000 0000

PMMODEL(5)

WAITB1

WAITB0

WAITM3

WAITM2

WAITM1

WAITM0

WAITE1

WAITE0

0000 0000

PMDOUT2H(5) Parallel Port Out Data High Byte (Buffer 3)

0000 0000

PMDOUT2L(5) Parallel Port Out Data Low Byte (Buffer 2)

0000 0000

PMDIN2H(5)

Parallel Port In Data High Byte (Buffer 3)

0000 0000

PMDIN2L(5)

Parallel Port In Data Low Byte (Buffer 2)

0000 0000

PMEH(5)

PTEN15

PTEN14

PTEN13

PTEN12

PTEN11

PTEN10

PTEN9

PTEN8

0000 0000

PMEL(5)

PTEN7

PTEN6

PTEN5

PTEN4

PTEN3

PTEN2

PTEN1

PTEN0

0000 0000

PMSTATH(5)

IBF

IBOV

—

IB3F

IB2F

IB1F

IB0F

00-- 0000

PMSTATL(5)

OBE

OBUF

—

OB3E

OB2E

OB1E

OB0E

10-- 1111

CVRCON

CVREN

CVROE

CVRR

r

CVR3

CVR2

CVR1

CVR0

0000 0000

TCLKCON

—

—T1RUN

—

T3CCP2

T3CCP1

---0 --00

DSGPR1

Deep Sleep Persistent General Purpose Register (contents retained even in Deep Sleep)

uuuu uuuu

DSGPR0

Deep Sleep Persistent General Purpose Register (contents retained even in Deep Sleep)

uuuu uuuu

DSCONH

DSEN

—

r

DSULPEN

RTCWDIS 0--- -000

DSCONL

—

ULPWDIS

DSBOR

RELEASE ---- -000

DSWAKEH

—

—DSINT0

---- ---0

DSWAKEL

DSFLT

—

DSULP

DSWDT

DSRTC

DSMCLR

DSPOR

0-00 00-1

TABLE 6-4:

REGISTER FILE SUMMARY (PIC18F46J50 FAMILY) (CONTINUED)

File Name

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Value on

POR, BOR

Details

on Page:

Legend:

x

= unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved. Bold indicates shared access SFRs.

Note

1:

Bit 21 of the PC is only available in Serial Programming (SP) modes.

2:

Reset value is ‘0’ when Two-Speed Start-up is enabled and ‘1’ if disabled.

3:

The SSPxMSK registers are only accessible when SSPxCON2<3:0> = 1001.

4:

Alternate names and definitions for these bits when the MSSP module is operating in I2C Slave mode. See Section 19.5.3.2 “Address

Masking Modes”

for details.

5:

These bits and/or registers are only available on 44-pin devices; otherwise, they are unimplemented and read as ‘0’. Reset values are

shown for 44-pin devices.

6:

The PMADDRH/PMDOUT1H and PMADDRL/PMDOUT1L register pairs share the same physical registers and addresses, but have

different functions determined by the module’s operating mode. See Section 11.1.2 “Data Registers” for more information.

7:

The TRISA6 and TRISA7 bits are only implemented when the pins are not configured for primary oscillator functions.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX6220ASA-5.0+T | IC VREF SERIES PREC 5V 8-SOIC |

| RPP20-4824DW-F | CONV DC/DC 20W 18-75VIN +/-24VOU |

| GCC31DCSH-S288 | CONN EDGECARD 62POS .100 EXTEND |

| XRP2525ID-1-F | IC PWR SW USB 3.0 SINGLE NSOIC8 |

| PCM16XV0 | PROCESSOR MODULE FOR 16F8XXA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCM-19 | 功能描述:電線鑒定 1.5" VINYL CLOTH #19 RoHS:否 制造商:TE Connectivity / Q-Cees 產(chǎn)品:Labels and Signs 類型: 材料:Vinyl 顏色:Blue 寬度:0.625 in 長度:1 in |

| PCM-1-9 | 制造商:Panduit Corp 功能描述:Cable Markers Vinyl Cloth White 制造商:Panduit Corp 功能描述:CBL ACC WIRE MARKER CARD VINYL CLOTH BLK/WHITE - Labels that come on sheets or rolls |

| PCM-190 | 功能描述:電線鑒定 Pre-Printed WM Card, Vinyl Cloth, .22" W RoHS:否 制造商:TE Connectivity / Q-Cees 產(chǎn)品:Labels and Signs 類型: 材料:Vinyl 顏色:Blue 寬度:0.625 in 長度:1 in |

| PCM-1900-06 | 制造商:PREMIER FARNELL 功能描述:6 NULL MODEM DB25 M/F CABLE |

| PCM-1900-1924 | 制造商:Panduit Corp 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。