- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382381 > PCF2105MU (NXP Semiconductors N.V.) LCD controller/driver PDF資料下載

參數(shù)資料

| 型號(hào): | PCF2105MU |

| 廠(chǎng)商: | NXP Semiconductors N.V. |

| 英文描述: | LCD controller/driver |

| 中文描述: | LCD控制器/驅(qū)動(dòng)器 |

| 文件頁(yè)數(shù): | 29/48頁(yè) |

| 文件大?。?/td> | 289K |

| 代理商: | PCF2105MU |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)當(dāng)前第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

1998 Jul 30

29

Philips Semiconductors

Product specification

LCD controller/driver

PCF2105

Notes

1.

2.

V

DD

= 5.0 V.

All timing values are valid within the operating supply voltage and ambient temperature range and are referenced to

V

IL

and V

IH

with an input voltage swing of V

SS

to V

DD

.

C

L

= total capacitance of one bus line in pF and R = 100

.

A fast mode I

2

C-bus device can be used in a standard-mode I

2

C-bus system, but the requirement t

SU;DAT

≥

250 ns

must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal.

If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line

t

r(max)

+ t

SU;DAT

= 1000 + 250 = 1250 ns (according to the standard-mode I

2

C-bus specification) before the SCL line

is released.

A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the V

IH(min)

of the SCL

signal) in order to bridge the undefined region of the falling edge of SCL.

The maximum t

HD;DAT

has only to be met if the device does not stretch t

LOW

of the SCL signal.

3.

4.

5.

6.

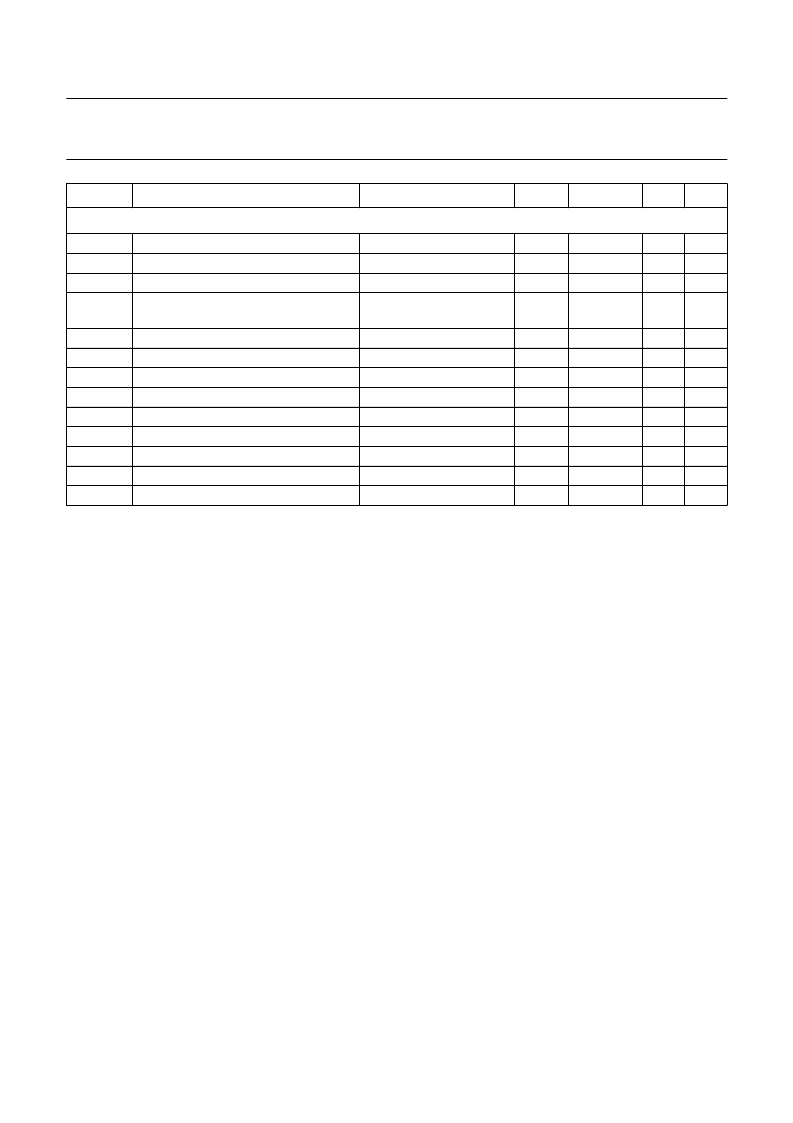

Timing characteristics: I

2

C-bus interface;

note 2; see Fig.25

f

SCL

t

SW

t

BUF

t

SU;STA

SCL clock frequency

tolerable spike width on bus

bus free time

set-up time for a repeated START

condition

START condition hold time

SCL LOW time

SCL HIGH time

SCL and SDA rise time

SCL and SDA fall time

data set-up time

data hold time

set-up time for STOP condition

load capacitance for each bus line

1.3

0.6

400

50

kHz

ns

μ

s

μ

s

t

HD;STA

t

LOW

t

HIGH

t

r

t

f

t

SU;DAT

t

HD;DAT

t

SU;STO

C

L

0.6

1.3

0.6

100

0

0.6

20 + RC

L

20 + RC

L

300

300

0.9

400

μ

s

μ

s

μ

s

ns

ns

ns

μ

s

μ

s

pF

note 3

note 3

note 4

notes 5 and 6

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCF26100 | Bluetooth Adapter IC |

| PCF26100ET | DVI_D - DVI_D SINGLE LINK CABLE 5M BLK RoHS Compliant: Yes |

| PCF3F10B | Analog IC |

| PCF3F160 | Analog IC |

| PCF3F30 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCF2105MU/2 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:LCD controller/driver |

| PCF2105MU/7 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:LCD Display Driver |

| PCF210AA | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:SPI Real time clock/calendar Time keeping application |

| PCF2110 | 制造商:未知廠(chǎng)家 制造商全稱(chēng):未知廠(chǎng)家 功能描述:LCD Display Driver |

| PCF2111 | 制造商:PHILIPS 制造商全稱(chēng):NXP Semiconductors 功能描述:LCD drivers |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。