- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD5003 (NXP Semiconductors N.V.) Advanced POCSAG Paging Decoder PDF資料下載

參數(shù)資料

| 型號(hào): | PCD5003 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Advanced POCSAG Paging Decoder |

| 中文描述: | 高級(jí)尋呼POCSAG碼解碼器 |

| 文件頁數(shù): | 14/44頁 |

| 文件大?。?/td> | 187K |

| 代理商: | PCD5003 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

1997 Jun 24

14

Philips Semiconductors

Product specification

Advanced POCSAG Paging Decoder

PCD5003

7.20

Battery condition input

A logic signal from an external sense circuit signalling

battery condition can be applied to the BAT input. This

input is sampled each time the receiver is disabled

(RXE

↓

0).

When enabled via the control register (D2 = 0), the

condition of input BAT is reflected in bit D6 of the status

register. Each change of state of bit D6 causes an external

interrupt at output INT.

When using the UAA2080 pager receiver a battery-low

condition corresponds to a logic HIGH-level. With a

different sense circuit the reverse polarity can be used as

well, because every change of state is signalled to an

external controller.

After a reset the initial condition of the battery-low indicator

in the status register is zero.

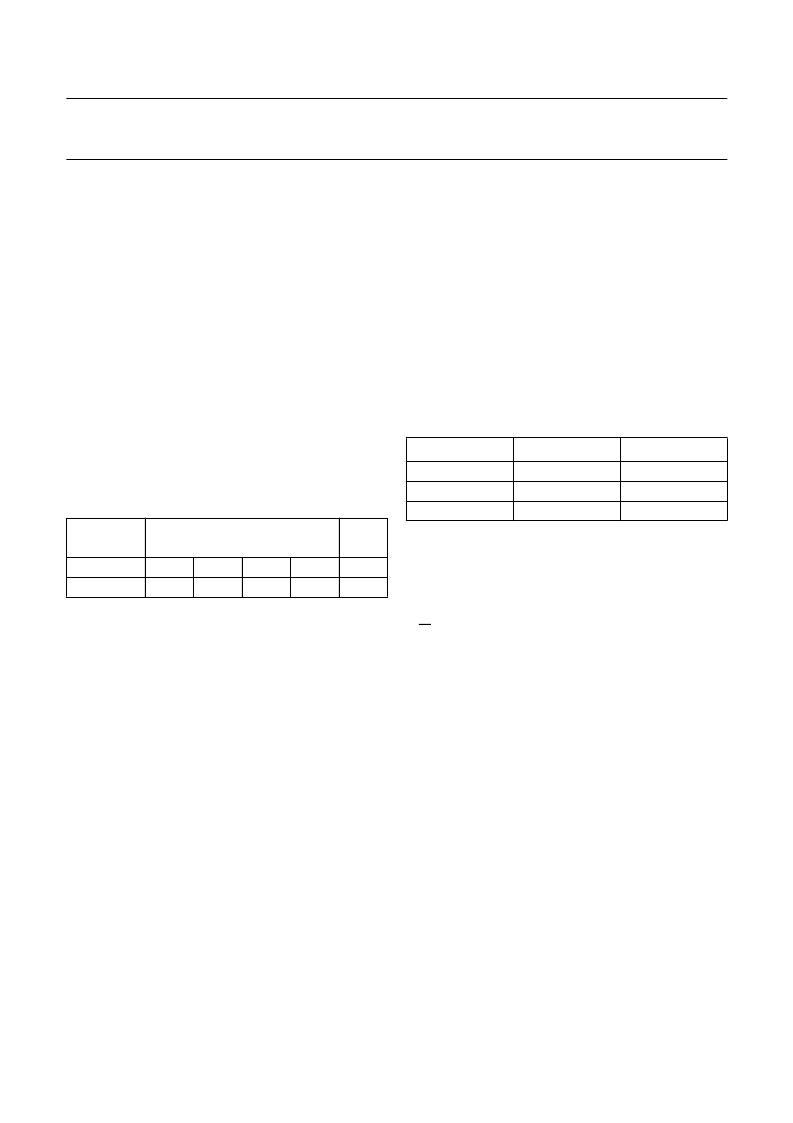

Table 11

Receiver and oscillator establishment times

(note 1)

Note

1.

The exact values may differ slightly from the above

values, depending on the bit rate (see Table 22).

7.21

Synthesizer control

Control of an external frequency synthesizer is possible

via a dedicated 3-line serial interface (outputs ZSD, ZSC

and ZLE). This interface is common to a number of

available synthesizers. The synthesizer is enabled using

the oscillator enable output ROE.

The frequency parameters must be programmed in

EEPROM. Two blocks of maximum 24 bits each can be

stored. Any unused bits must be programmed at the

beginning of a block: only the last bits are used by the

synthesizer.

When the function is selected by SPF programming

(SPF byte 01, bit D6), data is transferred to the

synthesizer each time the PCD5003 is switched from OFF

to ON status. Transfer takes place serially in two blocks,

starting with bit 0 (MSB) of block 1 (see Table 25).

Data bits on ZSD change on the falling flanks of ZSC. After

clocking all bits into the synthesizer, a latch enable pulse

CONTROL

OUTPUT

ESTABLISHMENT TIME

UNIT

RXE

ROE

5

10

30

15

40

30

50

ms

ms

20

copies the data to the internal divider registers. A timing

diagram is given in Fig.5.

The data output timing is synchronous, but has a pause in

the bit stream of each block. This pause occurs in the

13th bit while ZSC is LOW. The nominal pause duration t

p

depends on the programmed bit rate for data reception

and is shown in Table 12. The total duration of the 13th bit

is given by t

ZCL

+ t

p

.

A similar pause occurs between the first and the second

data block. The delay between the first latch enable pulse

and the second data block is given by t

ZDL2

+ t

p

.

The complete start-up timing of the synthesizer interface is

given in Fig.12.

Table 12

Synthesizer programming pause

7.22

Serial microcontroller interface

The PCD5003 has an I

2

C-bus serial microcontroller

interface capable of operating at 400 kbits/s.

The PCD5003 is a slave transceiver with a 7-bit I

2

C-bus

address 39 (bits A6 to A0 = 0100111). Together with the

R/W bit the first byte of an I

2

C-bus message then becomes

4EH (write) or 4FH (read).

Data transmission requires 2 lines: SDA (data) and SCL

(clock), each with an external pull-up resistor. The clock

signal (SCL) for any data transmission must be generated

by the external controlling device.

A transmission is initiated by a start condition

(S: SCL = 1, SDA =

↓

) and terminated by a stop condition

(P: SCL = 1, SDA =

↑

).

Data bits must be stable when SCL is HIGH. If there are

multiple transmissions, the stop condition can be replaced

with a new start condition.

Data is transferred on a byte basis, starting with a device

address and a read/write indicator. Each transmitted byte

must be followed by an acknowledge bit ACK

(active LOW). If a receiving device is not ready to accept

the next complete byte, it can force a bus wait state by

holding SCL LOW.

The general I

2

C-bus transmission format is shown in Fig.6.

Formats for master/slave communication are shown in

Fig.7.

BIT RATE (bit/s)

t

p

(clocks)

119

33

1

t

p

(

μ

s)

1549

430

13

512

1200

2400

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5003H | Advanced POCSAG Paging Decoder |

| PCD5008 | FLEX Pager Decoder |

| PCD5008H | FLEX Pager Decoder |

| PCD5013 | FLEX roaming decoder II |

| PCD5013H | FLEX roaming decoder II |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5003A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

| PCD5003AH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

| PCD5003H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5003HB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5003U/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。