- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382380 > PCD5003 (NXP Semiconductors N.V.) Advanced POCSAG Paging Decoder PDF資料下載

參數(shù)資料

| 型號: | PCD5003 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Advanced POCSAG Paging Decoder |

| 中文描述: | 高級尋呼POCSAG碼解碼器 |

| 文件頁數(shù): | 13/44頁 |

| 文件大?。?/td> | 187K |

| 代理商: | PCD5003 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

1997 Jun 24

13

Philips Semiconductors

Product specification

Advanced POCSAG Paging Decoder

PCD5003

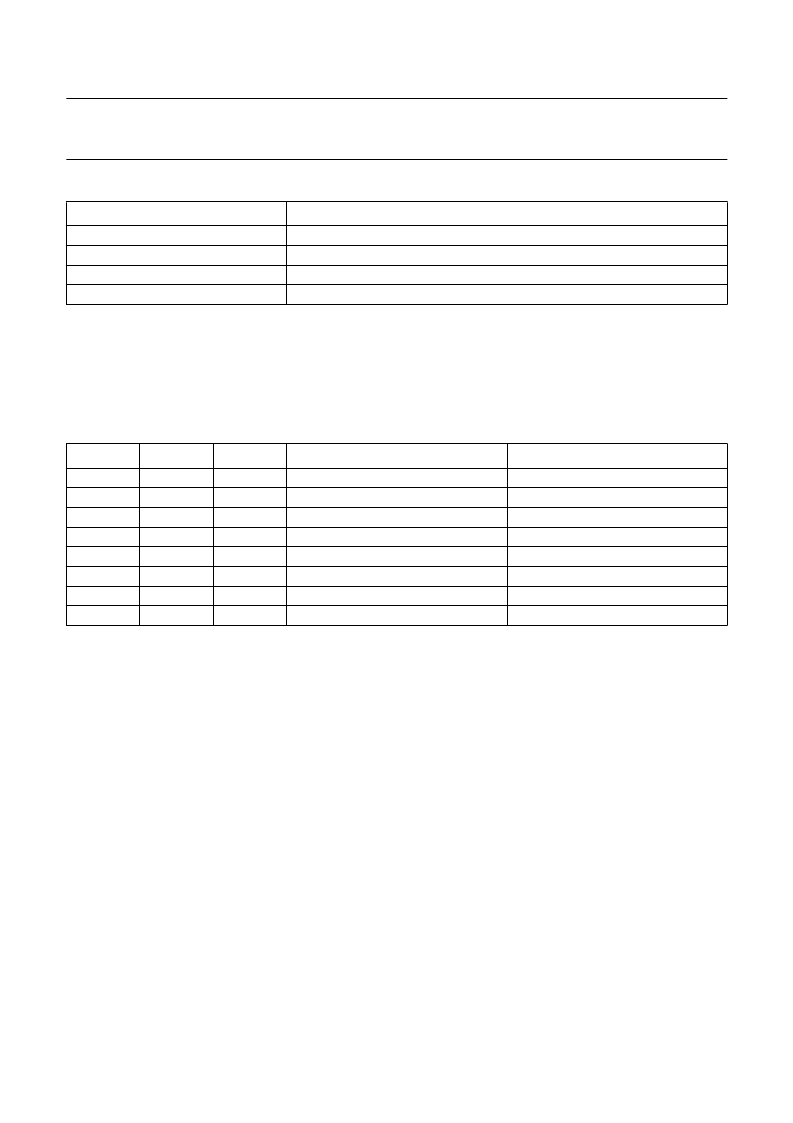

Table 9

Call terminator bit identification

Note

1.

The DF bit in the call terminator is set:

a) When any call data codeword in the terminating batch was uncorrectable, while in ‘data receive’ mode.

b) When the sync word at the start of the terminating batch did not match the standard POCSAG or a

user-programmed sync word, while in ‘data fail’ mode.

Table 10

Error type identification (note 1)

Note

1.

POCSAG code allows a maximum of 3 bit errors to be detected per codeword.

BITS (MSB to LSB)

IDENTIFICATION

FT

forced call termination (1 = yes)

identifier number of last sync word

data fail mode indication (1 = data fail mode); note 1

detected error type; see Table 10; E3 = 0 in a call terminator

S3 to S1

DF

E3 to E1

E3

E2

E1

ERROR TYPE

NUMBER OF ERRORS

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

no errors - correct codeword

parity bit in error

single bit error

single bit error and parity error

not used

4-bit burst error and parity error

2-bit random error

uncorrectable codeword

0

1

1 + parity

1

3 (e.g.1101)

2

3 or more

Successful call termination occurs by reception of a valid

address codeword with less than 2 bit errors.

Unsuccessful termination occurs when sync word is not

detected while in ‘data fail’ mode.

It is generally possible to distinguish these two conditions

using the sync word identifier number (bits S3 to S1); the

identifier number will be non-zero for correct termination,

and zero for sync word failure.

Only when a call is received in ‘data fail’ mode and the call

is terminated before the end of the batch, is it not possible

to distinguish unsuccessful from correct termination.

Reception of message data can be terminated at any time

by transmitting a forced call termination command to the

control register via the I

2

C-bus. Any call received will then

be terminated immediately and ‘data fail’ mode will be

entered.

7.18

Receiver and oscillator control

A paging receiver and an RF oscillator circuit can be

controlled independently via enable outputs RXE and ROE

respectively. Their operating periods are optimized

according to the synchronization mode of the decoder.

Each enable signal has its own programmable

establishment time (see Table 11).

7.19

External receiver control and monitoring

An external controller may enable the receiver control

outputs continuously via an I

2

C-bus command, overruling

the normal enable pattern. Data reception continues

normally. This mode can be left by means of a reset or an

I

2

C-bus command.

External monitoring of the receiver control output RXE is

possible via bit D6 in the status register, when enabled via

the control register (D2 = 1). Each change of state of

output RXE will generate an external interrupt at

output INT.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PCD5003H | Advanced POCSAG Paging Decoder |

| PCD5008 | FLEX Pager Decoder |

| PCD5008H | FLEX Pager Decoder |

| PCD5013 | FLEX roaming decoder II |

| PCD5013H | FLEX roaming decoder II |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PCD5003A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

| PCD5003AH | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Enhanced Pager Decoder for POCSAG |

| PCD5003H | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

| PCD5003HB-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Telecommunication Decoder |

| PCD5003U/10 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Advanced POCSAG Paging Decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。