- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382377 > PC89C660 (NXP Semiconductors N.V.) 80C51 8-bit Flash microcontroller family PDF資料下載

參數(shù)資料

| 型號: | PC89C660 |

| 廠商: | NXP Semiconductors N.V. |

| 元件分類: | 8位微控制器 |

| 英文描述: | 80C51 8-bit Flash microcontroller family |

| 中文描述: | 80C51的8位閃存微控制器系列 |

| 文件頁數(shù): | 15/89頁 |

| 文件大小: | 491K |

| 代理商: | PC89C660 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁

Philips Semiconductors

Product data

P89C660/P89C662/P89C664/

P89C668

80C51 8-bit Flash microcontroller family

16KB/32KB/64KB ISP/IAP Flash with 512B/1KB/2KB/8KB RAM

2002 Oct 28

15

Arbitration and Synchronization Logic

In the Master Transmitter mode, the arbitration logic checks that

every transmitted logic 1 actually appears as a logic 1 on the I

2

C

bus. If another device on the bus overrules a logic 1 and pulls the

SDA line low, arbitration is lost, and SIO1 immediately changes from

master transmitter to slave receiver. SIO1 will continue to output

clock pulses (on SCL) until transmission of the current serial byte is

complete.

Arbitration may also be lost in the Master Receiver mode. Loss of

arbitration in this mode can only occur while SIO1 is returning a “not

acknowledge: (logic 1) to the bus. Arbitration is lost when another

device on the bus pulls this signal LOW. Since this can occur only at

the end of a serial byte, SIO1 generates no further clock pulses.

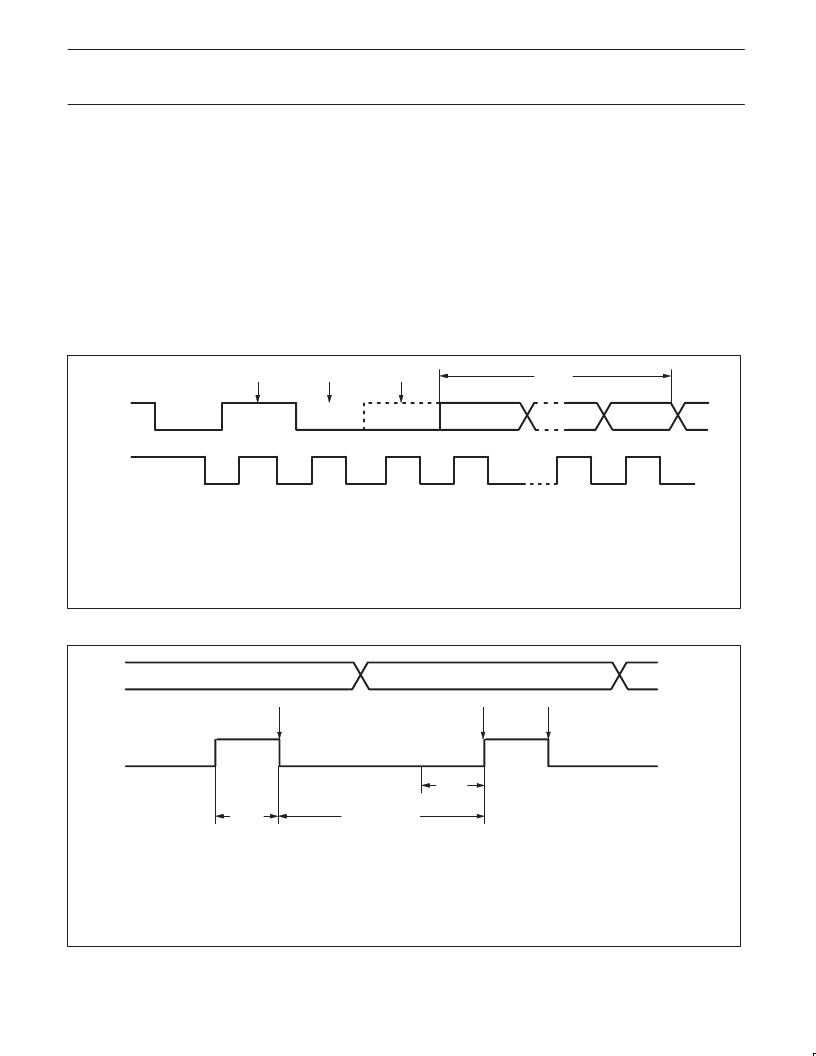

Figure 4 shows the arbitration procedure.

The synchronization logic will synchronize the serial clock generator

with the clock pulses on the SCL line from another device. If two or

more master devices generate clock pulses, the “mark” duration is

determined by the device that generates the shortest “marks,” and

the “space” duration is determined by the device that generates the

longest “spaces.” Figure 5 shows the synchronization procedure.

A slave may stretch the space duration to slow down the bus

master. The space duration may also be stretched for handshaking

purposes. This can be done after each bit or after a complete byte

transfer. SIO1 will stretch the SCL space duration after a byte has

been transmitted or received and the acknowledge bit has been

transferred. The serial interrupt flag (SI) is set, and the stretching

continues until the serial interrupt flag is cleared.

ACK

1. Another device transmits identical serial data.

SDA

1

2

3

4

8

9

SCL

(1)

(1)

(2)

(3)

2. Another device overrules a logic 1 (dotted line) transmitted by SIO1 (master) by pulling the SDA line low. Arbitration is

lost, and SIO1 enters the slave receiver mode.

3. SIO1 is in the slave receiver mode but still generates clock pulses until the current byte has been transmitted. SIO1 will

not generate clock pulses for the next byte. Data on SDA originates from the new master once it has won arbitration.

SU00967

Figure 4. Arbitration Procedure

(1)

SCL

(3)

(1)

SDA

MARK

DURATION

SPACE DURATION

(2)

1. Another service pulls the SCL line low before the SIO1 “mark” duration is complete. The serial clock generator is immediately

reset and commences with the “space” duration by pulling SCL low.

2. Another device still pulls the SCL line low after SIO1 releases SCL. The serial clock generator is forced into the wait state

until the SCL line is released.

3. The SCL line is released, and the serial clock generator commences with the mark duration.

SU00968

Figure 5. Serial Clock Synchronization

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| PC8D52 | |

| PC8Q52 | PHOTOCOUPLER |

| PC8Q66Q | |

| PC910 | |

| PC910L0NSZ | PHOTOCOUPLER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| PC89HK | 功能描述:HARDWARE KIT PD8010 9010DKN RoHS:是 類別:RF/IF 和 RFID >> RF配件 系列:* 標(biāo)準(zhǔn)包裝:1 系列:* |

| PC8ADVA2M49PXHSA1 | 制造商:Infineon Technologies AG 功能描述:PAYMENT - Bulk |

| PC8ADVAKM49XHSA2 | 制造商:Infineon Technologies AG 功能描述:PAYMENT - Rail/Tube |

| PC8ADVAKM51XHSA1 | 制造商:Infineon Technologies AG 功能描述:PAYMENT - Rail/Tube |

| PC8ADVAKM51XHSA2 | 制造商:Infineon Technologies AG 功能描述:PAYMENT - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。