- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄299575 > OR3T1256PS208I-DB (LATTICE SEMICONDUCTOR CORP) FPGA, 784 CLBS, 186000 GATES, PQFP208 PDF資料下載

參數(shù)資料

| 型號(hào): | OR3T1256PS208I-DB |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 784 CLBS, 186000 GATES, PQFP208 |

| 封裝: | PLASTIC, SQFP2-208 |

| 文件頁(yè)數(shù): | 36/203頁(yè) |

| 文件大?。?/td> | 1368K |

| 代理商: | OR3T1256PS208I-DB |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)

130

Lattice Semiconductor

Data Sheet

November 2006

ORCA Series 3C and 3T FPGAs

Timing Characteristics (continued)

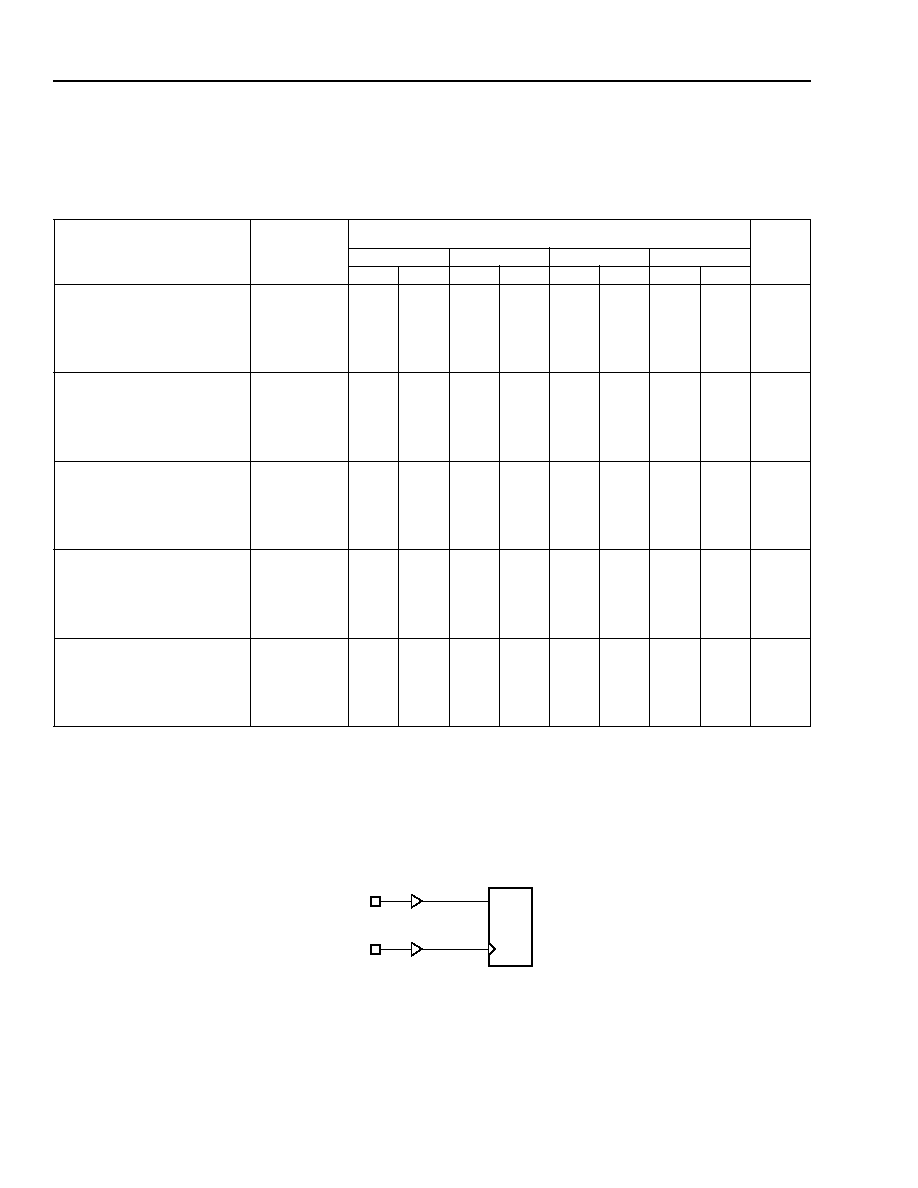

Table 59. OR3C/Txxx Input to General System Clock (SCLK) Setup/Hold Time (Pin-to-Pin)

OR3Cxx Commercial: VDD = 5.0 V ± 5%, 0 °C

< TA < 70 °C; Industrial: VDD = 5.0 V ± 10%, –40 °C < TA < +85 °C.

OR3Txxx Commercial: VDD = 3.0 V to 3.6 V, 0 °C

< TA < 70 °C; Industrial: VDD = 3.0 V to 3.6 V, –40 °C < TA < +85 °C.

Notes:

The pin-to-pin timing parameters in this table should be used instead of results reported by ispLEVER.

This clock delay is for a fully routed clock tree that uses the clock network. It includes both the input buffer delay and the clock routing to the PIO

FF CLK input. The delay will be reduced if any of the clock branches are not used. The given setup (delayed and no delay) and hold (delayed)

timing allows the input clock pin to be located in any PIO on any side of the device, but a PIO FF must be used. The hold (no delay) timing

assumes the clock pin is located at one of the four middle PICs on any side of the device and that a PIO FF is used. If the clock pin is located

elsewhere, then the last parameter in the table must be added to the hold (no delay) timing.

5-4847(F)

Figure 81. Input to System Clock Setup/Hold Time

Description

(TJ = 85 °C, VDD = min)

Device

Speed

Unit

-4

-5

-6

-7

Min

Max

Min

Max

Min

Max

Min

Max

Input to SCLK Setup Time

OR3T20

OR3T30

OR3T55

OR3C/T80

OR3T125

—

0.00

—

0.00

—

0.00

—

0.00

—

ns

Input to SCLK Setup Time

(delayed data input)

OR3T20

OR3T30

OR3T55

OR3C/T80

OR3T125

—

0.99

0.79

—

1.33

1.22

1.09

0.93

0.78

—

1.47

1.40

1.33

1.26

1.19

—

3.09

3.03

2.97

2.91

2.86

—

ns

Input to SCLK Hold Time

OR3T20

OR3T30

OR3T55

OR3C/T80

OR3T125

—

6.82

7.62

—

4.74

5.01

5.56

6.19

7.07

—

3.64

3.83

4.18

4.56

5.14

—

3.04

3.22

3.54

3.89

4.44

—

ns

Input to SCLK Hold Time

(delayed data input)

OR3T20

OR3T30

OR3T55

OR3C/T80

OR3T125

—

0.00

—

0.00

—

0.00

—

0.00

—

ns

Additional Hold Time if Non-

mid-PIC Used as SCLK Pin

(no delay on data input)

OR3T20

OR3T30

OR3T55

OR3C/T80

OR3T125

—

0.41

0.63

—

0.16

0.20

0.36

0.55

1.11

—

0.18

0.21

0.37

0.57

1.05

—

0.17

0.20

0.35

0.55

1.02

—

ns

Q

D

SCLK

INPUT

PIO FF

Select

devices

have

been

discontinued.

See

Ordering

Information

section

for

product

status.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| OR3T1256PS240-DB | FPGA, 784 CLBS, 186000 GATES, PQFP240 |

| OR3T1256PS240I-DB | FPGA, 784 CLBS, 186000 GATES, PQFP240 |

| OR3T1257PS208-DB | FPGA, 784 CLBS, 186000 GATES, PQFP208 |

| OR3T306S240I-DB | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

| OR3T307S240-DB | FPGA, 196 CLBS, 48000 GATES, PQFP240 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| OR3T125-6PS240 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T1256PS240-DB | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 6272 LUT 342 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR3T125-6PS240I | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

| OR3T1256PS240I-DB | 功能描述:FPGA - 現(xiàn)場(chǎng)可編程門(mén)陣列 6272 LUT 342 I/O RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| OR3T125-7BA352 | 制造商:AGERE 制造商全稱:AGERE 功能描述:3C and 3T Field-Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。