- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄224506 > MT58L512L18PS-7.5IT 512K X 18 CACHE SRAM, 4 ns, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | MT58L512L18PS-7.5IT |

| 元件分類: | SRAM |

| 英文描述: | 512K X 18 CACHE SRAM, 4 ns, PQFP100 |

| 封裝: | PLASTIC, MS-026BHA, TQFP-100 |

| 文件頁(yè)數(shù): | 19/32頁(yè) |

| 文件大小: | 616K |

| 代理商: | MT58L512L18PS-7.5IT |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)當(dāng)前第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)

26

8Mb: 512K x 18, 256K x 32/36 Pipelined, SCD SyncBurst SRAM

Micron Technology, Inc., reserves the right to change products or specifications without notice.

MT58L512L18P_2.p65 – Rev. 6/01

2001, Micron Technology, Inc.

8Mb: 512K x 18, 256K x 32/36

PIPELINED, SCD SYNCBURST SRAM

READ TIMING PARAMETERS

-5

-6

-7.5

-10

SYMBOL

MIN MAX MIN MAX MIN MAX MIN MAX UNITS

tKC

5.0

6.0

7.5

10

ns

fKF

200

166

133

100

MHz

tKH

2.0

2.3

2.5

3.0

ns

tKL

2.0

2.3

2.5

3.0

ns

tKQ

3.1

3.5

4.0

5.0

ns

tKQX

1.0

1.5

ns

tKQLZ

0

1.5

ns

tKQHZ

3.1

3.5

4.2

5.0

ns

tOEQ

3.1

3.5

4.2

5.0

ns

tOELZ

0000

ns

tOEHZ

3.0

3.5

4.2

4.5

ns

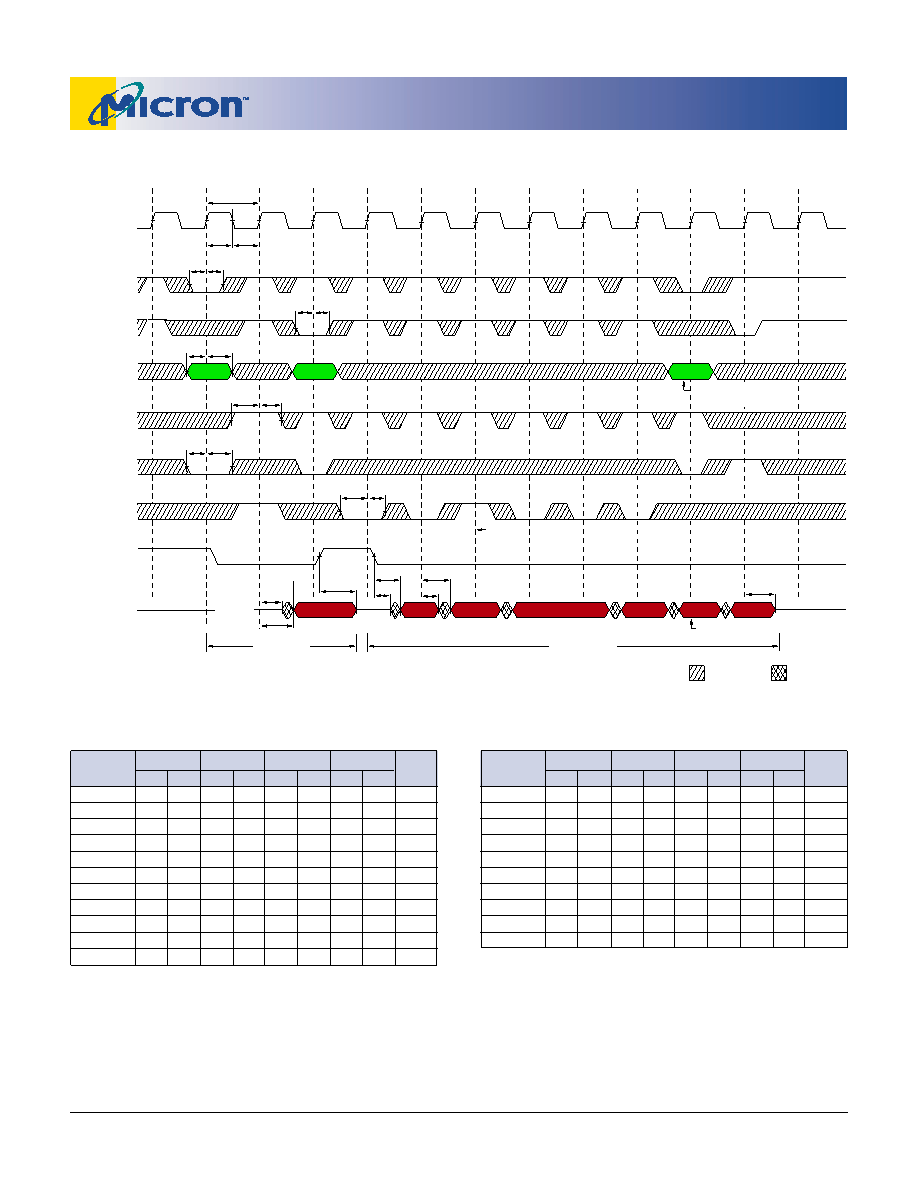

READ TIMING 3

tKC

tKL

CLK

ADSP#

tADSH

tADSS

ADDRESS

tKH

OE#

ADSC#

CE#

(NOTE 2)

tAH

tAS

A1

tCEH

tCES

GW#, BWE#,

BWa#-BWd#

Q

High-Z

tKQLZ

tKQX

tKQ

ADV#

tOEHZ

tKQ

Single READ

BURST READ

tOEQ

tOELZ

tKQHZ

ADV#

suspends

burst.

Burst wraps around

to its initial state.

tAAH

tAAS

tWH

tWS

tADSH

tADSS

Q(A2)

Q(A2 + 1)

Q(A2 + 2)

Q(A1)

Q(A2)

Q(A2 + 1)

Q(A2 + 3)

A2

A3

(NOTE 1)

Deselect

cycle.

(NOTE 3)

(NOTE 4)

Burst continued with

new base address.

DON’T CARE

UNDEFINED

NOTE: 1. Q(A2) refers to output from address A2. Q(A2 + 1) refers to output from the next internal burst address following A2.

2. CE2# and CE2 have timing identical to CE#. On this diagram, when CE# is LOW, CE2# is LOW and CE2 is HIGH. When

CE# is HIGH, CE2# is HIGH and CE2 is LOW.

3. Timing is shown assuming that the device was not enabled before entering into this sequence. OE# does not cause Q

to be driven until after the following clock rising edge.

4. Outputs are disabled within one clock cycle after deselect.

tAS

1.5

2.0

ns

tADSS

1.5

2.0

ns

tAAS

1.5

2.0

ns

tWS

1.5

2.0

ns

tCES

1.5

2.0

ns

tAH

0.5

ns

tADSH

0.5

ns

tAAH

0.5

ns

tWH

0.5

ns

tCEH

0.5

ns

-5

-6

-7.5

-10

SYMBOL

MIN MAX MIN MAX MIN MAX MIN MAX UNITS

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT78740 | RELAY SOCKET |

| MT78745 | RELAY SOCKET |

| MT9KDF12872PZ-1G6XX | 128M X 72 DDR DRAM MODULE, DMA240 |

| MTE-28-T | INTERCONNECTION DEVICE |

| MTE-11-T | INTERCONNECTION DEVICE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT58L512L18PT-10 | 制造商:Cypress Semiconductor 功能描述:512KX18 SRAM PLASTIC TQFP 3.3V 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT58L512L18PT-7.5 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| MT58L512L18PT-7.5 IT | 制造商:Cypress Semiconductor 功能描述:512KX18 SRAM PLASTIC IND TEMP |

| MT58L512V18F | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:8Mb: 512K x 18, 256K x 32/36 FLOW-THROUGH SYNCBURST SRAM |

| MT58L512V18P | 制造商:MICRON 制造商全稱:Micron Technology 功能描述:8Mb: 512K x 18, 256K x 32/36 PIPELINED, SCD SYNCBURST SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。