- 您現(xiàn)在的位置:買賣IC網 > PDF目錄45365 > MPC8377EVRANGA (FREESCALE SEMICONDUCTOR INC) 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 PDF資料下載

參數(shù)資料

| 型號: | MPC8377EVRANGA |

| 廠商: | FREESCALE SEMICONDUCTOR INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 |

| 封裝: | 31 X 31 MM, 2.46 MM HEIGHT, 1 MM PITCH, LEAD FREE, PLASTIC, BGA-689 |

| 文件頁數(shù): | 32/124頁 |

| 文件大小: | 1462K |

| 代理商: | MPC8377EVRANGA |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁

MPC8377E PowerQUICC II Pro Processor Hardware Specifications, Rev. 2

Freescale Semiconductor

15

RESET Initialization

5.2

RESET AC Electrical Characteristics

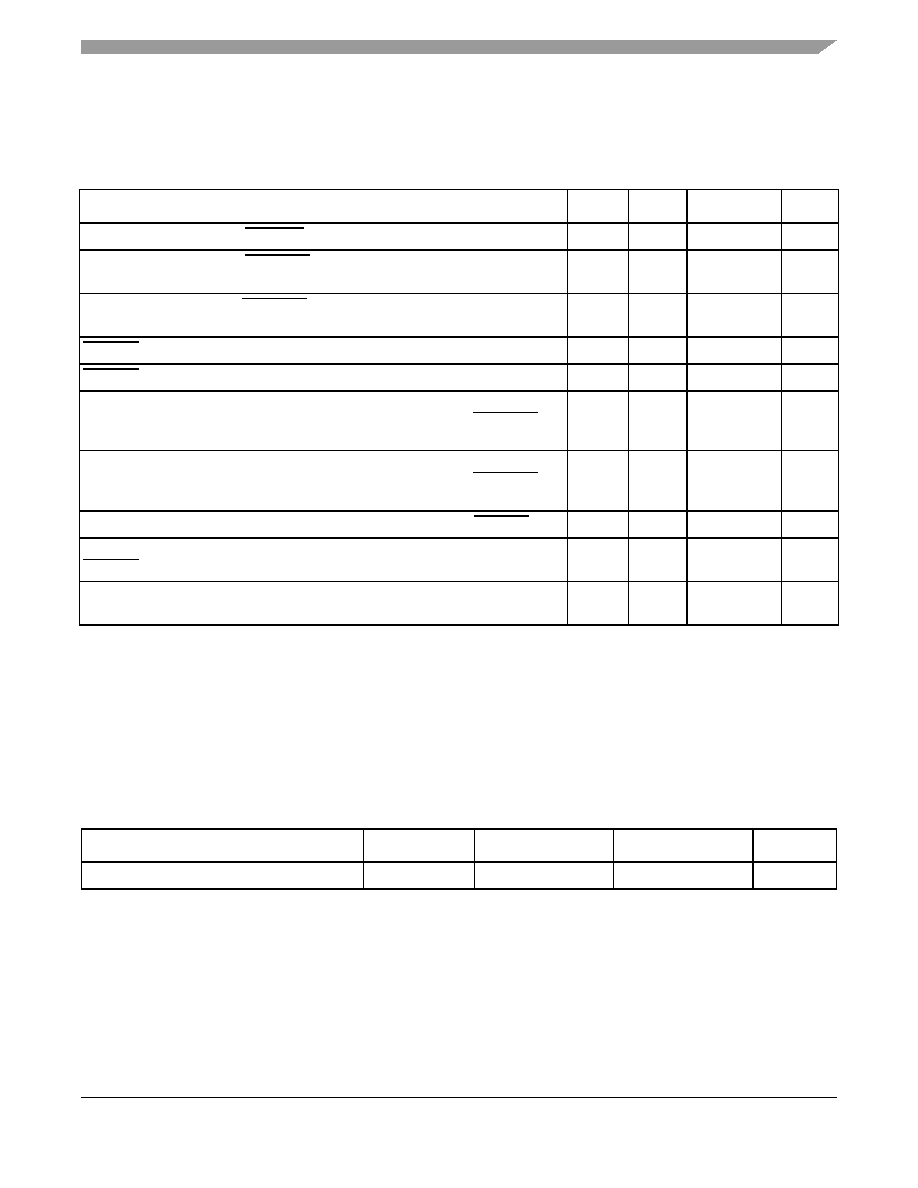

Table 10 provides the reset initialization AC timing specifications of the device.

Table 11 provides the PLL lock times.

Table 10. RESET Initialization Timing Specifications

Parameter/Condition

Min

Max

Unit

Notes

Required assertion time of HRESET to activate reset flow

32

—

tPCI_SYNC_IN

Required assertion time of PORESET with stable clock applied to CLKIN when

the device is in PCI host mode

32

—

tCLKIN

Required assertion time of PORESET with stable clock applied to PCI_CLK when

the device is in PCI agent mode

32

—

tPCI_SYNC_IN

HRESET assertion (output)

512

—

tPCI_SYNC_IN

HRESET negation to negation (output)

16

—

tPCI_SYNC_IN

Input setup time for POR config signals (CFG_RESET_SOURCE[0:3],

CFG_CLKIN_DIV, and CFG_LBMUX) with respect to negation of PORESET

when the device is in PCI host mode

4—

tCLKIN

2

Input setup time for POR config signals (CFG_RESET_SOURCE[0:3],

CFG_CLKIN_DIV, and CFG_LBMUX) with respect to negation of PORESET

when the device is in PCI agent mode

4—

tPCI_SYNC_IN

Input hold time for POR config signals with respect to negation of HRESET

0—

ns

—

Time for the device to turn off POR config signals with respect to the assertion of

HRESET

—4

ns

Time for the device to start driving functional output signals multiplexed with the

POR configuration signals with respect to the negation of HRESET

1—

tPCI_SYNC_IN

Note:

1 t

PCI_SYNC_IN is the clock period of the input clock applied to PCI_SYNC_IN. When the device is In PCI host mode the primary

clock is applied to the CLKIN input, and PCI_SYNC_IN period depends on the value of CFG_CLKIN_DIV. See the

MPC8379E

Integrated Host Processor Reference Manual for more details.

2 t

CLKIN is the clock period of the input clock applied to CLKIN. It is only valid when the device is in PCI host mode. See the

MPC8379E Integrated Host Processor Reference Manual for more details.

3 POR config signals consists of CFG_RESET_SOURCE[0:3], CFG_LBMUX, and CFG_CLKIN_DIV.

Table 11. PLL Lock Times

Parameter

Min

Max

Unit

Notes

PLL lock times

—

100

μs—

Note:

The device guarantees the PLL lock if the clock settings are within spec range. The core clock also depends on the core PLL

ratio. See Section 23, “Clocking,” for more information.

相關PDF資料 |

PDF描述 |

|---|---|

| MPC8378ECVRALGA | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378ECVRAGFA | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378ECVRAGGA | 32-BIT, 400 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378ECVRALFA | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA689 |

| MPC8378ECVRANFA | 32-BIT, 333 MHz, MICROPROCESSOR, PBGA689 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| MPC8377EWLANA | 功能描述:開發(fā)板和工具包 - 其他處理器 MPC8377EWLANA, KIT RoHS:否 制造商:Freescale Semiconductor 產品:Development Systems 工具用于評估:P3041 核心:e500mc 接口類型:I2C, SPI, USB 工作電源電壓: |

| MPC8377EWLANB | 功能描述:WiFi/802.11模塊 KIT RoHS:否 制造商:Taiyo Yuden 支持協(xié)議:802.11 b/g/n 頻帶: 數(shù)據速率:150 Mbps 接口類型:SDIO 傳輸功率(最大): 天線連接器類型: 工作電源電壓:3.4 V to 5.5 V 傳輸供電電流: 接收供電電流: 最大工作溫度:+ 80 C 尺寸:35 mm x 15 mm x 2.9 mm |

| MPC8377EZQAFDA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8377EZQAFFA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

| MPC8377EZQAFGA | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:PowerQUICC? II Pro Processor Hardware Specifications |

發(fā)布緊急采購,3分鐘左右您將得到回復。