- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄299472 > MC68HC11FC0CFU5 (MOTOROLA INC) Technical Summary 8-Bit Microcontroller PDF資料下載

參數(shù)資料

| 型號: | MC68HC11FC0CFU5 |

| 廠商: | MOTOROLA INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Technical Summary 8-Bit Microcontroller |

| 中文描述: | 8-BIT, 6 MHz, MICROCONTROLLER, PQFP64 |

| 封裝: | QFP-64 |

| 文件頁數(shù): | 46/74頁 |

| 文件大?。?/td> | 513K |

| 代理商: | MC68HC11FC0CFU5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當(dāng)前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁

MOTOROLA

MC68HC11F1/FC0

50

MC68HC11FTS/D

10.2 SPI Registers

U = Unaffected by reset

SPIE — SPI Interrupt Enable

When SPI interrupts are enabled, a hardware interrupt sequence is requested each time the SPIF or

MODF status flag is set. SPI interrupts are inhibited if this bit is cleared or if the I bit in the condition code

register is one.

0 = SPI interrupt disabled

1 = SPI interrupt enabled

SPE — SPI Enable

When the SPE bit is set, PD[5:2] are dedicated to the SPI function. If the SPI is in master mode and the

DDRD bit 5 is set, then PD5/SS becomes a general-purpose output instead of the SS input.

0 = SPI off

1 = SPI on

DWOM — Port D Wired-OR Mode Option for SPI Pins PD[5:2]

0 = Normal CMOS outputs

1 = Open-drain outputs

MSTR — Master Mode Select

0 = Slave mode

1 = Master mode

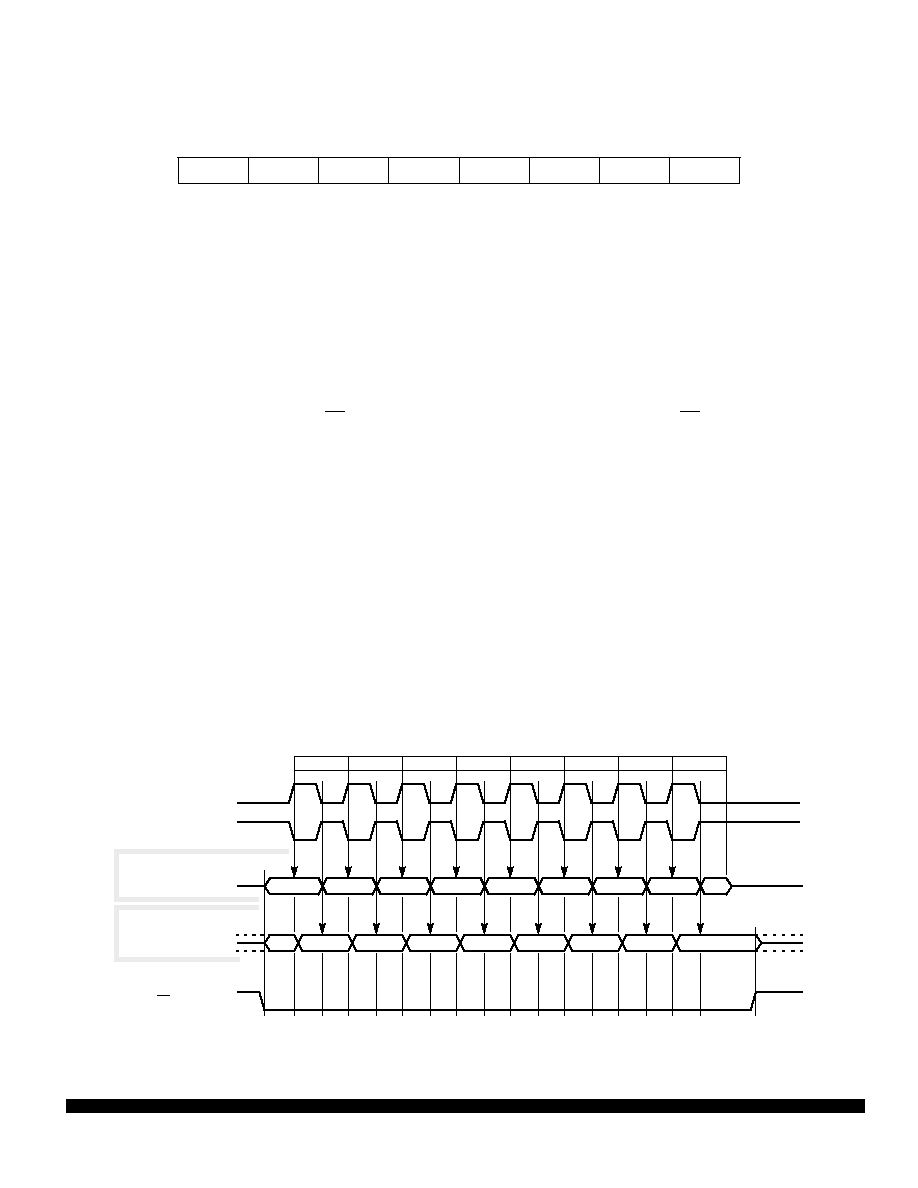

CPOL — Clock Polarity

When the clock polarity bit is cleared and data is not being transferred, the SCK pin of the master device

has a steady state low value. When CPOL is set, SCK idles high. Refer to Figure 13.

CPHA — Clock Phase

The clock phase bit, in conjunction with the CPOL bit, controls the clock-data relationship between mas-

ter and slave. The CPHA bit selects one of two clocking protocols. Refer to Figure 13.

Figure 13 SPI Data Clock Timing Diagram

SPCR — SPI Control Register

$x028

Bit 7

6

5

4

3

2

1

Bit 0

SPIE

SPE

DWOM

MSTR

CPOL

CPHA

SPR1

SPR0

RESET:

0

1

U

SCK CYCLE #

(FOR REFERENCE)

12345678

SCK (CPOL = 0)

SCK (CPOL = 1)

(CPHA = 0) DATA OUT

(CPHA = 1) DATA OUT

SS (TO SLAVE)

SAMPLE INPUT

MSB

654321

LSB

MSB

654321

LSB

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC68L11FC0PU3 | Technical Summary 8-Bit Microcontroller |

| MC68L11FC0PU4 | Technical Summary 8-Bit Microcontroller |

| MC74A6-3.3T | DIGITAL TEMP SENSOR-SERIAL, 8BIT(s), 3Cel, RECTANGULAR, THROUGH HOLE MOUNT |

| MC74F37DR2 | F/FAST SERIES, QUAD 2-INPUT NAND GATE, PDSO14 |

| MC74HC4851ADR2 | 8-CHANNEL, SGL ENDED MULTIPLEXER, PDSO16 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MC68HC11FC0CPU4 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11FC0CPU5 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11FC0FU6 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11FC0PU6 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:Technical Summary 8-Bit Microcontroller |

| MC68HC11G5 | 制造商:FREESCALE 制造商全稱:Freescale Semiconductor, Inc 功能描述:High-density Complementary Metal Oxide Semiconductor (HCMOS) Microcontroller Unit |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。