M68HC11

REFERENCE MANUAL

MAIN TIMER AND REAL-TIME INTERRUPT

MOTOROLA

10-15

back to TFLG2. The condition of the other flags in the register is not important, even if

they become set in the middle of the BCLR instruction, because the write cycle of the

instruction will write zeros to all bits except those corresponding to flags that are to be

cleared. Writing a zero to a bit corresponding to a flag that is set does not disturb the

flag.

It is not appropriate to use the bit set (BSET) instruction to clear flags in the timer flag

registers because this could inadvertently clear one or more of the other flags in the

register. Again, consider the case of clearing the TOF bit. Suppose RTIF is set after

the TOF interrupt is recognized but before the BSET instruction is started. The BSET

instruction is a read-modify-write instruction that reads the operand, ORs this with a

mask having ones in the bit(s) to be set, and writes the resulting value back to the op-

erand address. Using this instruction on TFLG1 or TFLG2 will clear all flags that are

set at the time the operand (in this case, the TFLG2 register) is read.

There are many instruction sequences that can be used to clear timer flags. In general,

each sequence takes a different number of bytes of object code and a different number

of cycles of execution time. The best sequence depends on a number of factors, in-

cluding (but not limited to) whether the user wants minimum execution time or mini-

mum program memory space. In many cases, the subtle differences in program size

and execution time are unimportant, and any of the sequences shown would be equal-

ly acceptable. Some sequences require registers to be in the direct addressing mode

memory space ($0000–$00FF), which is not practical in many applications. Since oth-

er sequences use indexed addressing, their efficiency will depend on whether or not

the index register already points to the register space (extra instructions and time are

required if the index register has to be changed).

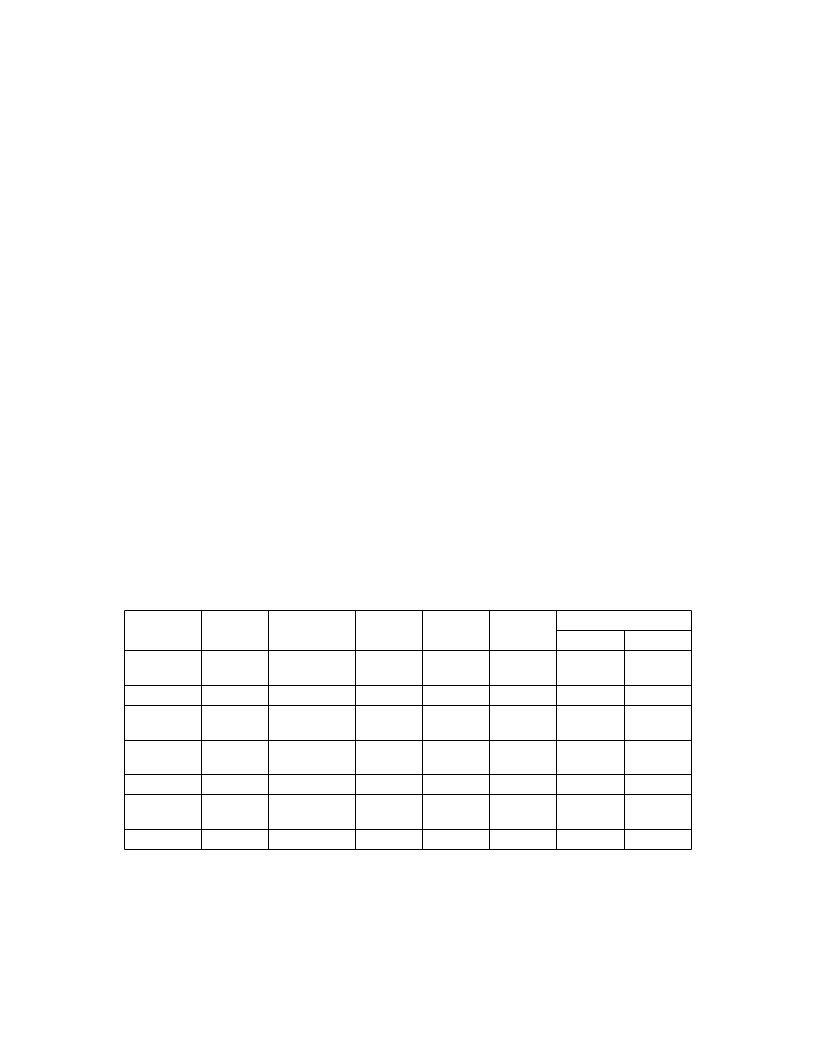

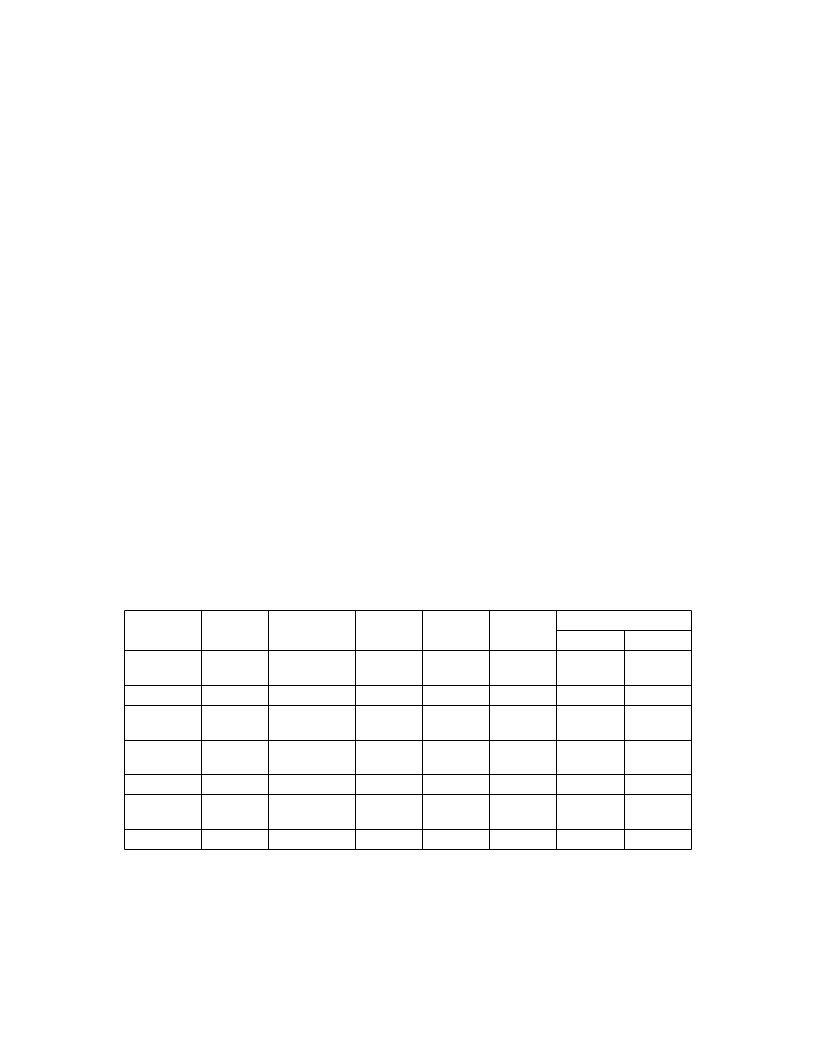

Table 10-4

illustrates seven different

instruction sequences that could be used to clear the TOF status bit in TFLG2.

10.3 Input-Capture Functions

Each input-capture function includes a 16-bit latch, input edge-detection logic, and in-

terrupt generation logic. The 16-bit latch captures the current value of the free-running

counter when a selected edge is detected at the corresponding timer input pin. The

Table 10-4 Instruction Sequences To Clear TOF

Instruction

Sequence

Opcode

Operand(s)

Address

Mode

Bytes

Cycles

Total Sequence

Bytes

Cycles

1

LDAA

STAA

BCLR

LDAA

STAA

LDAA

STAA

BCLR

LDAA

STAA

BCLR

#$80

<TFLG2

<TFLG2 $7F

#$80

TFLG2

#$80

TFLG2,X

TFLG2,X $7F

#$80

TFLG2,Y

TFLG2,Y $7F

(IMM)

(DIR)

(DIR)

(IMM)

(EXT)

(IMM)

(IND,X)

(IND,X)

(IMM)

(IND,Y)

(IND,Y)

2

2

3

2

3

2

2

3

2

3

4

2

3

6

2

4

2

4

7

2

5

8

4

5

2

3

6

3

5

6

4

4

6

5

3

7

6

5

7

7

4

8