- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382289 > MB90246APFV (FUJITSU LTD) 16-bit Proprietary Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | MB90246APFV |

| 廠商: | FUJITSU LTD |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 16-bit Proprietary Microcontroller |

| 中文描述: | 16-BIT, MROM, 16 MHz, MICROCONTROLLER, PQFP100 |

| 封裝: | PLASTIC, LQFP-100 |

| 文件頁(yè)數(shù): | 36/100頁(yè) |

| 文件大小: | 1956K |

| 代理商: | MB90246APFV |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)當(dāng)前第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)

36

MB90246A Series

5. 16-bit Re-load Timer

The 16-bit re-load timer has an internal clock mode for counting down in synchronization to three types of internal

clocks and an event count mode for counting down detecting a given edge of the pulse input to the external bus

pin, and either of the two functions can be selectively used.

For this timer, an “underflow” is defined as the timing of transition from the counter value of “0000

H

” to “FFFF

H

”.

According to this definition, an underflow occurs after [re-load register setting value + 1] counts.

In operating the counter, the re-load mode for repeating counting operation after re-loading a counter value after

an underflow or the one-shot mode for stopping the counting operation after an underflow can be selectively used.

Because the timer can generate an interrupt upon an underflow, the timer conforms to the extended intelligent

I/O service (EI

2

OS).

The MB90246A series has 3 channels of 16-bit re-load timers.

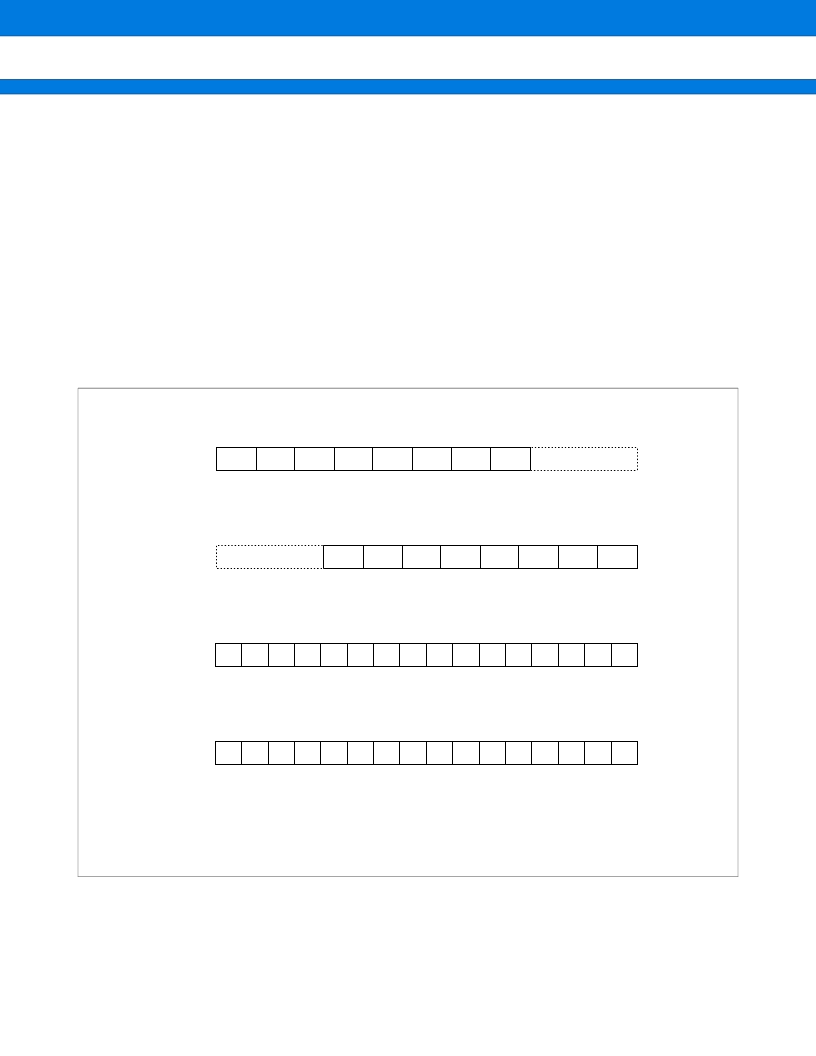

(1) Register Configuration

Initial value

XXXXXXXX

B

XXXXXXXX

B

XXXXXXXX

B

bit 7. . . . . . . . . . . . .

Timer control status register 0, 1, 2 upper digits (TMCSR0, TMCSR1, TMCSR2: H)

Address

TMCSR0 : 000041

H

TMCSR1 : 000049

H

TMCSR2 : 000051

H

—

—

—

—

—

—

—

CSL1

CSL0

MOD2 MOD1

(TMCSR : L)

—

R/W

R/W

R/W

R/W

bit 15

bit 14

bit 13

bit 12

bit 11

bit 10

bit 9

bit 8

Initial value

- - - -0000

B

bit 1. . . . . . . . . . . . .

Timer control status register 0, 1, 2 lower digits (TMCSR0, TMCSR1, TMCSR2: L)

Address

TMCSR0 : 000040

H

TMCSR1 : 000048

H

TMCSR2 : 000050

H

R/W

OUTE

MOD0

(TMCSR : H)

R/W

R/W

R/W

R/W

R/W

R/W

R/W

bit 7

bit 6

bit 5

bit 4

Initial value

00000000

B

RELD

OUTL

UF

INTE

TRG

CNTE

bit 3

bit 2

bit 1

bit 0

16-bit timer register 0, 1 (TMR0, TMR1, TMR2)

Address

bit 15

TMR0 : 000042

H

TMR1 : 00004A

H

TMR2 : 000052

H

Initial value

XXXXXXXX

B

XXXXXXXX

B

XXXXXXXX

B

bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

R

16-bit re-load register 0, 1 (TMRL0,TMRL1)

Address

bit 15bit 14bit 13bit 12bit 11bit 10 bit 9 bit 8 bit 7 bit 6 bit 5 bit 4 bit 3 bit 2 bit 1 bit 0

TMRLR0 : 000044

H

TMRLR1 : 00004C

H

TMRLR2 : 000054

H

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

W

R/W : Readable and writable

R : Read only

W : Write only

— : Unused

X : Indeterminate

D15 D14 D13 D12 D11 D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

D15 D14 D13 D12 D11 D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MB91FV130CR-ES | 32-Bit RISC Microcontroller |

| MB91F133PBT | 32-Bit RISC Microcontroller |

| MB91133PBT | 32-Bit RISC Microcontroller |

| MB91F133PMT2 | 32-Bit RISC Microcontroller |

| MB91133 | 32-Bit RISC Microcontroller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MB90330 | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

| MB90330A | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:16-bit Microcontroller |

| MB90330A_9E | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:16-bit microcontrollers |

| MB90333A | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:16-bit Microcontroller |

| MB90333APFF | 制造商:FUJITSU 制造商全稱(chēng):Fujitsu Component Limited. 功能描述:16-bit Proprietary Microcontroller |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。