- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385520 > MAX104CHC (MAXIM INTEGRATED PRODUCTS INC) 【5V, 1Gsps, 8-Bit ADC with On-Chip 2.2GHz Track/Hold Amplifier PDF資料下載

參數(shù)資料

| 型號: | MAX104CHC |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | ADC |

| 英文描述: | 【5V, 1Gsps, 8-Bit ADC with On-Chip 2.2GHz Track/Hold Amplifier |

| 中文描述: | 1-CH 8-BIT FLASH METHOD ADC, PARALLEL ACCESS, PBGA192 |

| 封裝: | 25 X 25 MM, ESBGA-192 |

| 文件頁數(shù): | 15/32頁 |

| 文件大小: | 637K |

| 代理商: | MAX104CHC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁當(dāng)前第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

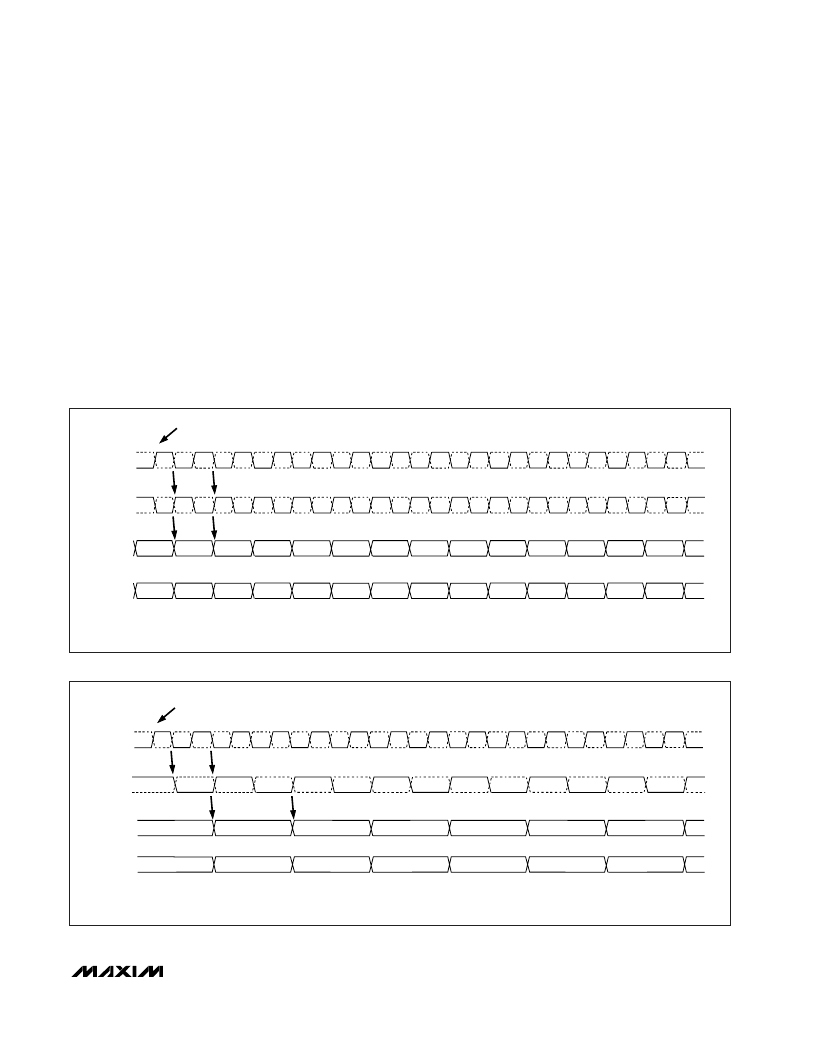

Non-Demultiplexed DIV1 Mode

The MAX104 may be operated at up to 500Msps in non-

demultiplexed DIV1 mode (Table 2). In this mode, the

internal demultiplexer is disabled, and sampled data is

presented to the primary port only, with the data repeat-

ed at the auxiliary port but delayed by one clock cycle

(Figure 6). Since the auxiliary output port contains the

same data stream as the primary output port, the auxil-

iary port can be shut down to save power by connecting

AUXEN1 and AUXEN2 to digital ground (GNDD). This

powers down the internal bias cells and causes both

outputs (true and complementary) of the auxiliary port to

pull up to a logic-high level. To save additional power,

the external 50

termination resistors connected to the

PECL termination power supply (V

CC

O - 2V) may be

removed from all auxiliary output ports.

Demultiplexed DIV2 Mode

The MAX104 features an internally selectable DIV2

mode (Table 2) that reduces the output data rate to

one-half of the sample clock rate. The demultiplexed

outputs are presented in dual 8-bit format with two con-

secutive samples appearing in the primary and auxil-

iary output ports on the rising edge of the data-ready

clock (Figure 7). The auxiliary data port contains the

previous sample, and the primary output contains the

most recent data sample. AUXEN1 and AUXEN2 must

be connected to V

CC

O to power-up the auxiliary port

PECL output drivers.

M

±5V, 1Gsps, 8-Bit ADC with

On-Chip 2.2GHz Trac k/Hold Amplifier

______________________________________________________________________________________

15

NOTE:

THE AUXILIARY PORT DATA IS DELAYED ONE ADDITIONAL CLOCK CYCLE FROM THE PRIMARY PORT DATA.

GROUNDING AUXEN1 AND AUXEN2 WILL POWER DOWN THE AUXILIARY PORT TOSAVE POWER.

CLK-

CLK+

n

n+1

n+2

n+3

n+4

n+5

n+1

n+2

n+3

n+4

n

n+1

n+2

n+3

n+4

n+5

n+6

n+7

n+8

n+9

n+10

n+11

n+12

n+13

ADC SAMPLE NUMBER

ADC SAMPLES ON THE RISING EDGE OF CLK+

CLK

DREADY

AUXILIARY

DATA PORT

PRIMARY

DATA PORT

DREADY+

DREADY-

Figure 6. Non-Demuxed, DIV1-Mode Timing Diagram

NOTE:

THE LATENCY TOTHE PRIMARY PORT IS 7.5 CLOCK CYCLES, AND THE LATENCY TOTHE AUXILIARY PORT IS 8.5 CLOCK CYCLES.

BOTH THE PRIMARY AND AUXILIARY DATA PORTS ARE UPDATED ON THE RISING EDGE OF THE DREADY+ CLOCK.

CLK-

CLK+

n

n+1

n+2

n+3

n+4

n+5

n+1

n-1

n+3

n+6

n+7

n+8

n+9

n+10

n+11

n+12

n+13

ADC SAMPLE NUMBER

ADC SAMPLES ON THE RISING EDGE OF CLK+

CLK

DREADY

AUXILIARY

DATA PORT

PRIMARY

DATA PORT

DREADY+

DREADY-

n

n+2

n+4

Figure 7. Demuxed DIV2-Mode Timing Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MAX105 | Dual, 6-Bit, 800Msps ADC with On-Chip, Wideband Input Amplifier |

| MAX105ECS | Dual, 6-Bit, 800Msps ADC with On-Chip, Wideband Input Amplifier |

| MAX1067ACEE | Multichannel, 14-Bit, 200ksps Analog-to-Digital Converters |

| MAX1067AEEE | Multichannel, 14-Bit, 200ksps Analog-to-Digital Converters |

| MAX1067BCEE | Multichannel, 14-Bit, 200ksps Analog-to-Digital Converters |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MAX104CHC-D | 制造商:Maxim Integrated Products 功能描述:ADC SGL FLASH 1GSPS 8BIT PARALLEL 192PIN ESBGA - Trays |

| MAX104CHC-TD | 制造商:Maxim Integrated Products 功能描述:ADC SGL FLASH 1GSPS 8BIT PARALLEL 192PIN ESBGA - Tape and Reel |

| MAX104EVKIT | 制造商:Maxim Integrated Products 功能描述:KIT PKG - Bulk |

| MAX105 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Dual, 6-Bit, 800Msps ADC with On-Chip, Wideband Input Amplifier |

| MAX1057 | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:10-Bit, Multichannel ADCs/DACs with FIFO, Temperature Sensing, and GPIO Ports |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。