- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98006 > M37510E6-FS 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CQCC160 PDF資料下載

參數(shù)資料

| 型號: | M37510E6-FS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, UVPROM, 8 MHz, MICROCONTROLLER, CQCC160 |

| 封裝: | WINDOWED, GLASS SEALED, LCC-160 |

| 文件頁數(shù): | 33/43頁 |

| 文件大?。?/td> | 614K |

| 代理商: | M37510E6-FS |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當(dāng)前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

39

7510 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

MITSUBISHI MICROCOMPUTERS

Symbol

tw(RESET)

tc(XIN)

twH(XIN)

twL(XIN)

tc(CNTR)

twH(CNTR)

twH(INT)

twL(CNTR)

twL(INT)

tc(SCLK1)

tc(SCLK2)

twH(SCLK1)

twH(SCLK2)

twL(SCLK1)

twL(SCLK2)

tsu(RXD1–SCLK1)

tsu(RXD2–SCLK2)

th(SCLK1–RXD1)

th(SCLK2–RXD2)

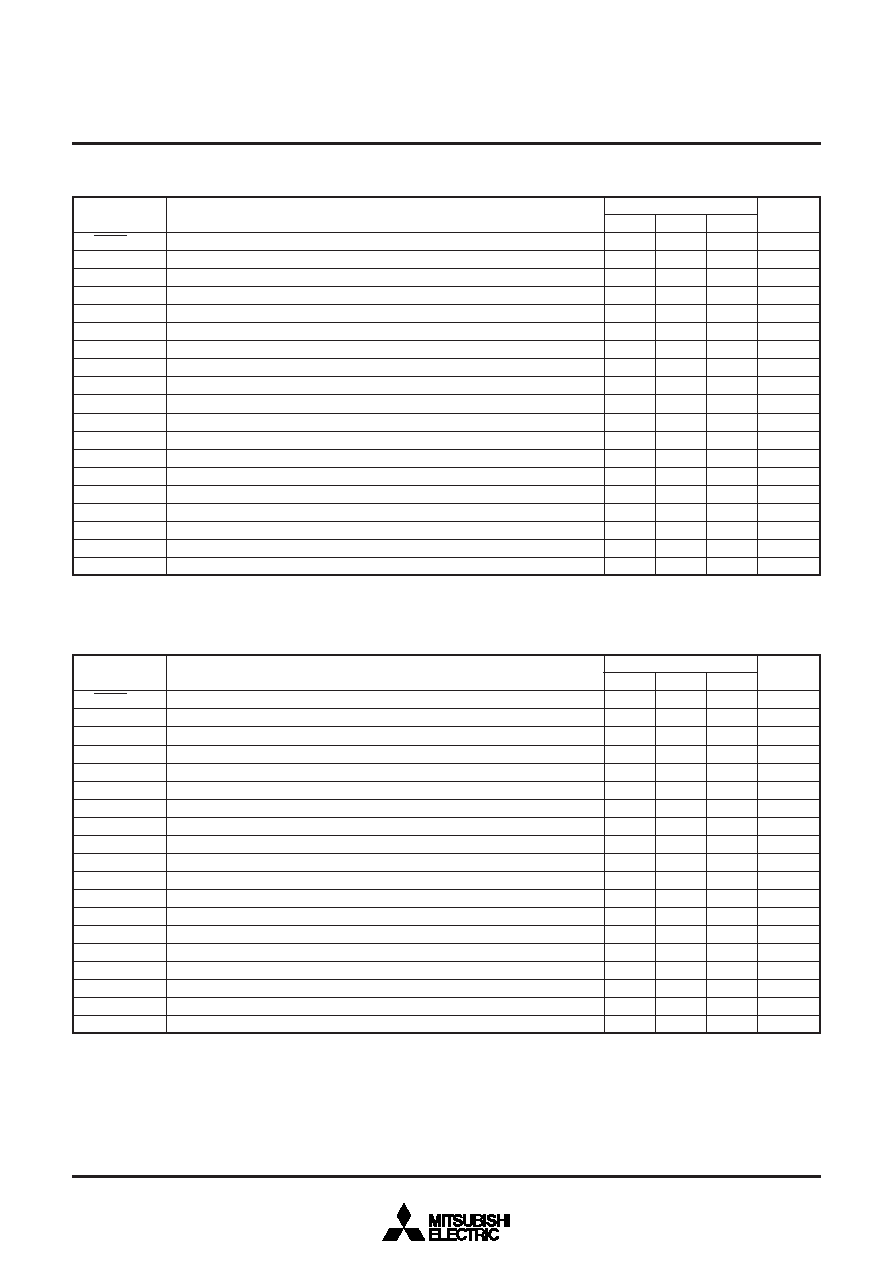

TIMING REQUIREMENTS 1 (VCC = 4.0 to 5.5 V, VSS = 0 V, Ta = –20 to 85

°C, unless otherwise noted)

Parameter

Reset input “L” pulse width

External clock input cycle time

External clock input “H” pulse width

External clock input “L” pulse width

CNTR0, CNTR1 input cycle time

CNTR0, CNTR1 input “H” pulse width

INT0, INT1 input “H” pulse width

CNTR0, CNTR1 input “L” pulse width

INT0, INT1 input “L” pulse width

Serial I/O1 clock input cycle time (Note)

Serial I/O2 clock input cycle time (Note)

Serial I/O1 clock input “H” pulse width (Note)

Serial I/O2 clock input “H” pulse width (Note)

Serial I/O1 clock input “L” pulse width (Note)

Serial I/O2 clock input “L” pulse width (Note)

Serial I/O1 input set up time

Serial I/O2 input set up time

Serial I/O1 input hold time

Serial I/O2 input hold time

Limits

Min.

2

125

50

200

80

800

370

220

100

Typ.

Max.

Unit

s

ns

Note: When f(

φ) = 4 MHz and bit 6 of address 001A16 or 003216 is “1” (clock synchronous). Divide this value by four when f(φ) = 4 MHz and bit 6 of address

001A16 or 003216 is “0” (clock asynchronous).

Symbol

tw(RESET)

tc(XIN)

twH(XIN)

twL(XIN)

tc(CNTR)

twH(CNTR)

twH(INT)

twL(CNTR)

twL(INT)

tc(SCLK1)

tc(SCLK2)

twH(SCLK1)

twH(SCLK2)

twL(SCLK1)

twL(SCLK2)

tsu(RXD1–SCLK1)

tsu(RXD2–SCLK2)

th(SCLK1–RXD1)

th(SCLK2–RXD2)

TIMING REQUIREMENTS 2 (VCC = 3.0 to 5.5 V, VSS = 0 V, Ta = –20 to 85

°C, unless otherwise noted)

Parameter

Reset input “L” pulse width

External clock input cycle time

External clock input “H” pulse width

External clock input “L” pulse width

CNTR0, CNTR1 input cycle time

CNTR0, CNTR1 input “H” pulse width

INT0, INT1 input “H” pulse width

CNTR0, CNTR1 input “L” pulse width

INT0, INT1 input “L” pulse width

Serial I/O1 clock input cycle time (Note)

Serial I/O2 clock input cycle time (Note)

Serial I/O1 clock input “H” pulse width (Note)

Serial I/O2 clock input “H” pulse width (Note)

Serial I/O1 clock input “L” pulse width (Note)

Serial I/O2 clock input “L” pulse width (Note)

Serial I/O1 input set up time

Serial I/O2 input set up time

Serial I/O1 input hold time

Serial I/O2 input hold time

Limits

Min.

2

500

200

500

230

2000

950

400

200

Typ.

Max.

Unit

s

ns

Note: When f(

φ) = 1 MHz and bit 6 of address 001A16 or 003216 is “1” (clock synchronous). Divide this value by four when f(φ) = 1 MHz and bit 6 of address

001A16 or 003216 is “0” (clock asynchronous).

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M37510E6-XXXFP | 8-BIT, OTPROM, 4 MHz, MICROCONTROLLER, PQFP176 |

| M37516M6H-XXXKP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 |

| M37516M4H-XXXKP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 |

| M37516M6H-XXXKP | 8-BIT, MROM, 4 MHz, MICROCONTROLLER, PQFP44 |

| M37532E8FP | 8-BIT, OTPROM, 6 MHz, MICROCONTROLLER, PDSO36 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M37510E7156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510E8156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M1156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M2156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

| M37510M3156FP | 制造商:MITSUBISHI 制造商全稱:Mitsubishi Electric Semiconductor 功能描述:SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。