- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄358765 > LC78625 (Sanyo Electric Co.,Ltd.) SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs PDF資料下載

參數(shù)資料

| 型號: | LC78625 |

| 廠商: | Sanyo Electric Co.,Ltd. |

| 元件分類: | 數(shù)字信號處理 |

| 英文描述: | SigmaDSP 28-/56-Bit Audio Processor with Two ADCs and Four DACs |

| 中文描述: | SigmaDSP的28-/56-Bit音頻處理器雙ADC和4個DAC |

| 文件頁數(shù): | 16/35頁 |

| 文件大?。?/td> | 440K |

| 代理商: | LC78625 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁

No. 5502-16/35

LC78625E

Internal brake modes

Code

COMMAND

RES = L

$C5

Internal brake on

$C4

Internal brake off

G

G

$A3

Internal brake CONT

$CB

Internal brake continuous mode

$CA

Reset continuous mode

G

G

$CD

TON mode during internal braking

$CC

Reset TON mode

G

G

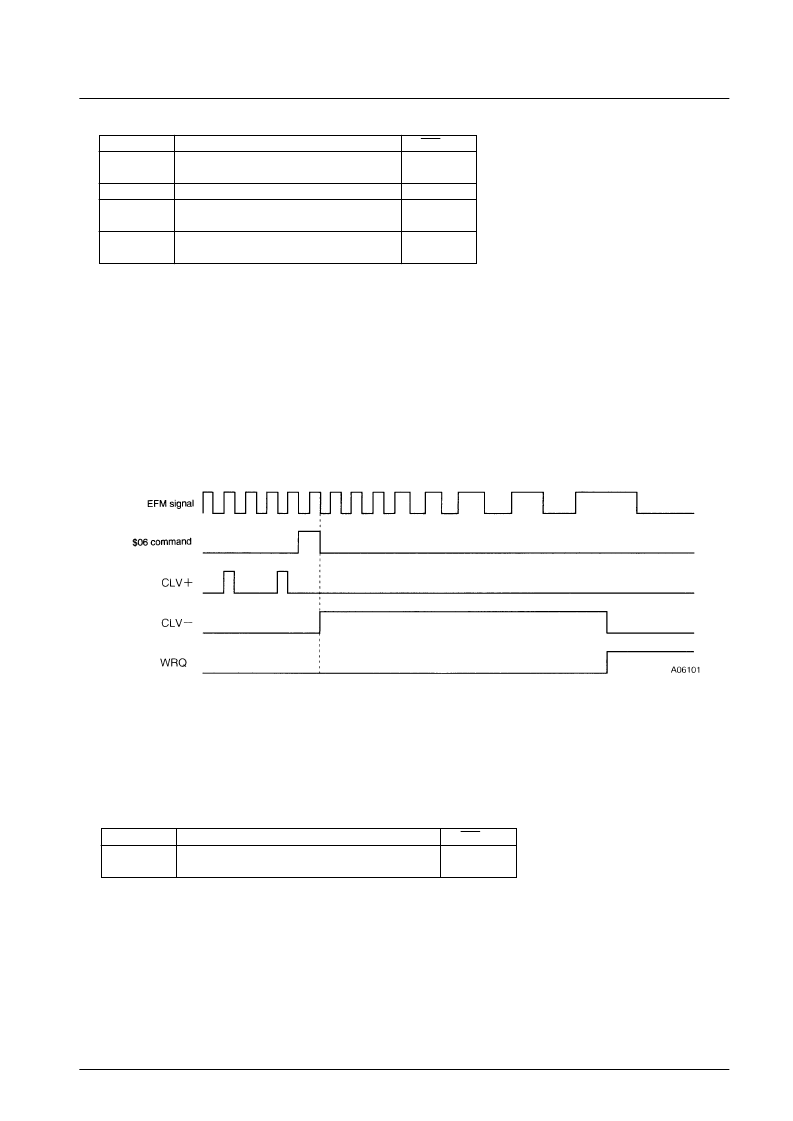

— Issuing the internal brake on command ($C5) sets the LC78625E to internal brake mode. In this mode, the disc

deceleration state can be monitored from the WRQ pin when a brake command ($06) is executed.

— In this mode the disc deceleration state is determined by counting the EFM signal density in a single frame, and

when the EFM signal count falls under four, the CLV–pin is dropped to low. At the same time the WRQ signal,

which functions as a brake completion monitor, goes high. When the microprocessor detects a high level on the

WRQ signal, it should issue a STOP command to fully stop the disc. In internal brake continuous mode, the CLV–

pin high-level output braking operation continues even after the WRQ brake completion monitor goes high.

Note that if errors occur in deceleration state determination due to noise in the EFM signal, the problem can be

rectified by changing the EFM signal count from four to eight with the internal brake control command ($A3).

— In internal braking TON mode, the TOFF pin is held low during internal brake operations. We recommend using

this feature, since it is effective at preventing incorrect detection at the disc mirror surface.

Note:

If focus is lost during the execution of an internal brake command, the pickup must first be refocussed and then the internal brake command must

be reissued.

Since incorrect deceleration state determination is possible depending on the EFM signal playback state (e.g., disc defects, access in progress), we

recommend using these functions in combination with a microprocessor.

8. Track jump circuit; Pin 19: HFL, pin 20: TES, pin 23: TOFF, pin 24: TGL, pin 25: THLD, pin 28: JP+, pin 29: JP–

The LC78625E supports the two track count modes listed below.

The earlier track count function uses the TES signal directly as the internal track counter clock.

To reduce counting errors resulting from noise on the rising and falling edges of the TES signal, the new track count

function prevents noise induced errors by using the combination of the TES and HFL signals, and implements a more

reliable track count function. However, dirt and scratches on the disc can result in HFL signal dropouts that may result

in missing track count pulses. Thus care is required when using this function.

Code

COMMAND

RES = L

$22

New track count mode (using the TES/HFL combination)

G

G

$23

Previous track count mode (directly counts the TES signal)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LC78626KE | Compact Disc Player DSP(用于CD播放器的8位DSP) |

| LC78626 | 16-bit fixed point DSP with Flash |

| LC78626E | 16-bit fixed point DSP with Flash |

| LC78628 | 16-bit fixed point DSP with Flash |

| LC78628E | 16-bit fixed point DSP with Flash |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LC78625E | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Compact Disc Player DSP |

| LC78626 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:DSP for Compact Disk Players |

| LC78626E | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:DSP for Compact Disk Players |

| LC78626KE | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:CD-Player Processor/Controller |

| LC78628 | 制造商:SANYO 制造商全稱:Sanyo Semicon Device 功能描述:Compact Disc Player DSP with Built-in HDCD Decoder |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。