- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄16240 > KS8695X-EVAL (Micrel Inc)BOARD EVAL EXPERIMENT KS8695X PDF資料下載

參數(shù)資料

| 型號: | KS8695X-EVAL |

| 廠商: | Micrel Inc |

| 文件頁數(shù): | 14/39頁 |

| 文件大?。?/td> | 0K |

| 描述: | BOARD EVAL EXPERIMENT KS8695X |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 相關(guān)產(chǎn)品: | KS8695X-ND - IC SWITCH 10/100 5PORT 208PQFP |

| 其它名稱: | 576-1005 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁當(dāng)前第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁

October 2004

21

M9999-102604

KS8695X

Micrel

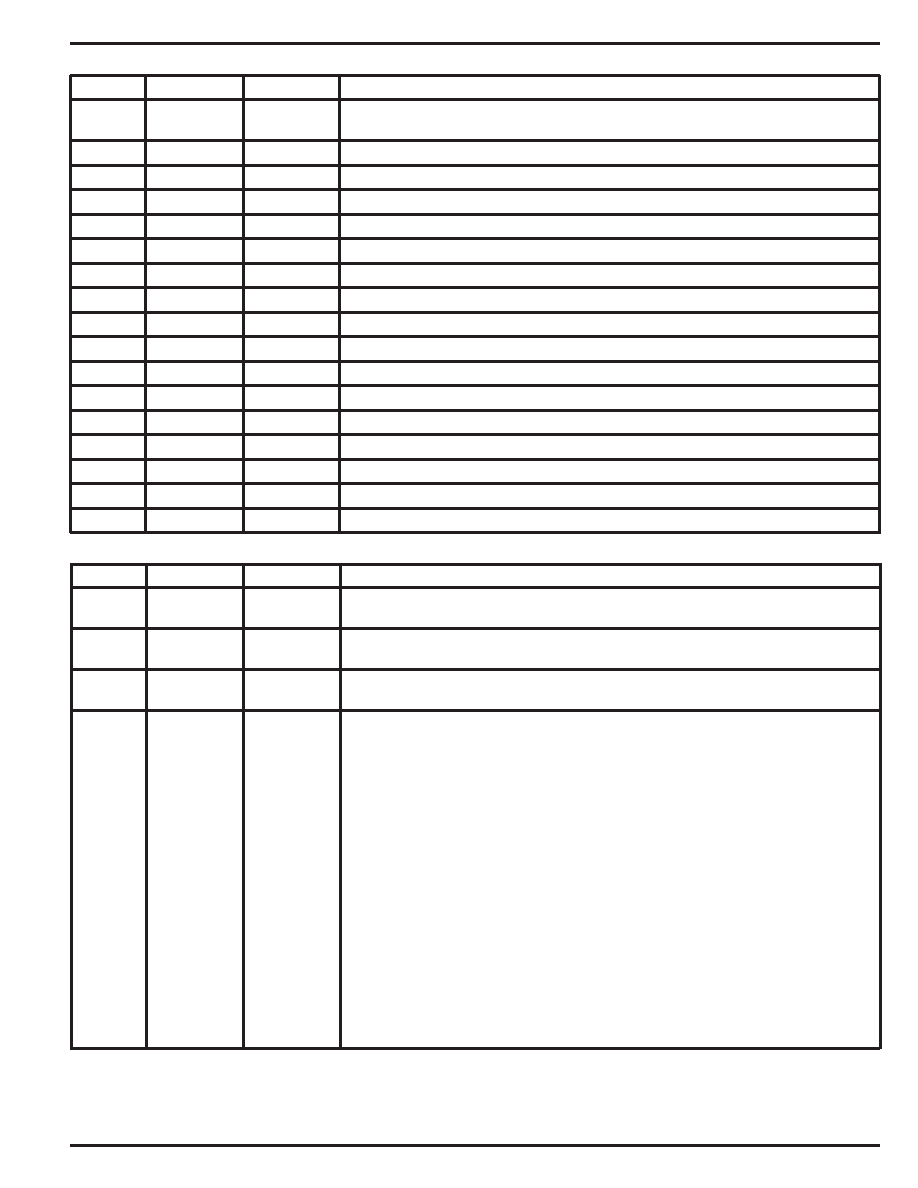

Reserved Pins

Pin

Name

I/O Type(1)

Description

84

TEST3

NC

The Reserved Pins serve as no connect in order to ensure correct operation of

the device. DO NOT connect any signal to these pins.

130

TEST4

NC

No connect.

131

TEST5

NC

No connect.

132

TEST6

NC

No connect.

133

TEST7

NC

No connect.

134

TEST8

NC

No connect.

135

TEST9

NC

No connect.

136

TEST10

NC

No connect.

139

TEST11

NC

No connect.

140

TEST12

NC

No connect.

141

TEST13

NC

No connect.

142

TEST14

NC

No connect.

143

TEST15

NC

No connect.

144

TEST16

NC

No connect.

145

TEST17

NC

No connect.

146

TEST18

NC

No connect.

147

TEST19

NC

No connect.

Advanced Memory Interface (SDRAM/ROM/FLASH/SRAM/EXTERNAL I/O)

24

SDICLK

I

SDRAM Clock In: SDRAM clock input for the SDRAM memory controller interface.

23

SDOCLK

O

System/SDRAM Clock Out: Output of the internal system clock, it is also used as the

clock signal for SDRAM interface.

205

ADDR21/BA1

O

Address Bit 21/Bank Address Input 1: Address bit 21 for asynchronous accesses.

Bank Address Input bit 1 for SDRAM accesses.

206

ADDR20/BA0

O

Address Bit 20/Bank Address Input 0: Address bit 20 for asynchronous accesses.

Bank Address Input bit 0 for SDRAM accesses.

198

ADDR[19]

O

Address Bus: The 22-bit address bus (including ADDR[21:20] above) covers 4M word

199

ADDR[18]

memory space shared by ROM/SRAM/FLASH, SDRAM, and external I/O banks.

200

ADDR[17]

During the SDRAM cycles, the internal address bus is used to generate RAS and

201

ADDR[16]

CAS addresses for the SDRAM. The number of column address bits in the SDRAM

202

ADDR[15]

banks can be programmed from 8 to 11 bits via the SDRAM control registers.

203

ADDR[14]

ADDR[12:0] are the SDRAM address, and ADDR[21:20] are the SDRAM bank

204

ADDR[13]

address. During other cycles, the ADDR[21:0] is the byte address of the data transfer.

207

ADDR[12]

Note: The address pinout non-sequential by design. It is optimized for board level

208

ADDR[11]

connections to SDRAM.

3

ADDR[10]

4

ADDR[9]

5

ADDR[8]

6

ADDR[7]

7

ADDR[6]

8

ADDR[5]

9

ADDR[4]

10

ADDR[3]

13

ADDR[2]

14

ADDR[1]

15

ADDR[0]

Note:

1. I = Input.

O = Output.

NC = No connect.

For SDRAM and ROM/SRAM/Flash, connect ADDR[0] to A0 on the memory,

ADDR[1] to A1 on the memory, and so forth. Address bit mapping for 8-bit,

16-bit, 32-bit access.

For external I/O devices, the system designer must connect address lines

conventionally for 8-bit, 16-bit, and 32-bit access.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VE-J74-EZ-F1 | CONVERTER MOD DC/DC 48V 25W |

| EET-ED2W331DA | CAP ALUM 330UF 450V 20% SNAP |

| RSM08DSES | CONN EDGECARD 16POS .156 EYELET |

| EET-UQ2W391LA | CAP ALUM 390UF 450V 20% SNAP |

| RBM15DSES | CONN EDGECARD 30POS .156 EYELET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| KS86C4004 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SAM87Ri family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-pr |

| KS86C4104 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SAM87Ri family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-pr |

| KS86C4204 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SAM87Ri family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-pr |

| KS86C4208 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SAM87Ri family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-pr |

| KS86C4302 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:SAM87Ri family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU, a wide range of integrated peripherals, and various mask-pr |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。