- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45383 > IT80C52EXXX-30SHXXX:R (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | IT80C52EXXX-30SHXXX:R |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| 文件頁數(shù): | 18/60頁 |

| 文件大小: | 5137K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當(dāng)前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

25

8266D-MCU Wireless-06/12

ATmega128RFA1

8.4.3 EEDR – EEPROM Data Register

Bit

7

6

5

4

3

2

1

0

$20 ($40)

EEDR7:0

EEDR

Read/Write

RW

Initial Value

0

For the EEPROM write operation, the EEDR Register contains the data to be written to

the EEPROM in the address given by the EEAR Register. For the EEPROM read

operation, the EEDR contains the data read out from the EEPROM at the address given

by EEAR.

Bit 7:0 – EEDR7:0 - EEPROM Data

8.4.4 EECR – EEPROM Control Register

Bit

7

6

5

4

3

2

1

0

$1F ($3F)

Res1

Res0

EEPM1

EEPM0

EERIE

EEMPE

EEPE

EERE

EECR

Read/Write

R

RW

Initial Value

0

X

0

X

0

Bit 7:6 – Res1:0 - Reserved

Bit 5:4 – EEPM1:0 - EEPROM Programming Mode

The EEPROM Programming mode bit setting defines which programming action will be

triggered when writing EEPE. It is possible to program data in one atomic operation

(erase the old value and program the new value) or to split the Erase and Write

operations in two different operations. While EEPE is set, any write to EEPM1:0 will be

ignored. During reset, the EEPM1:0 bits will be reset to 0 unless the EEPROM is busy

programming.

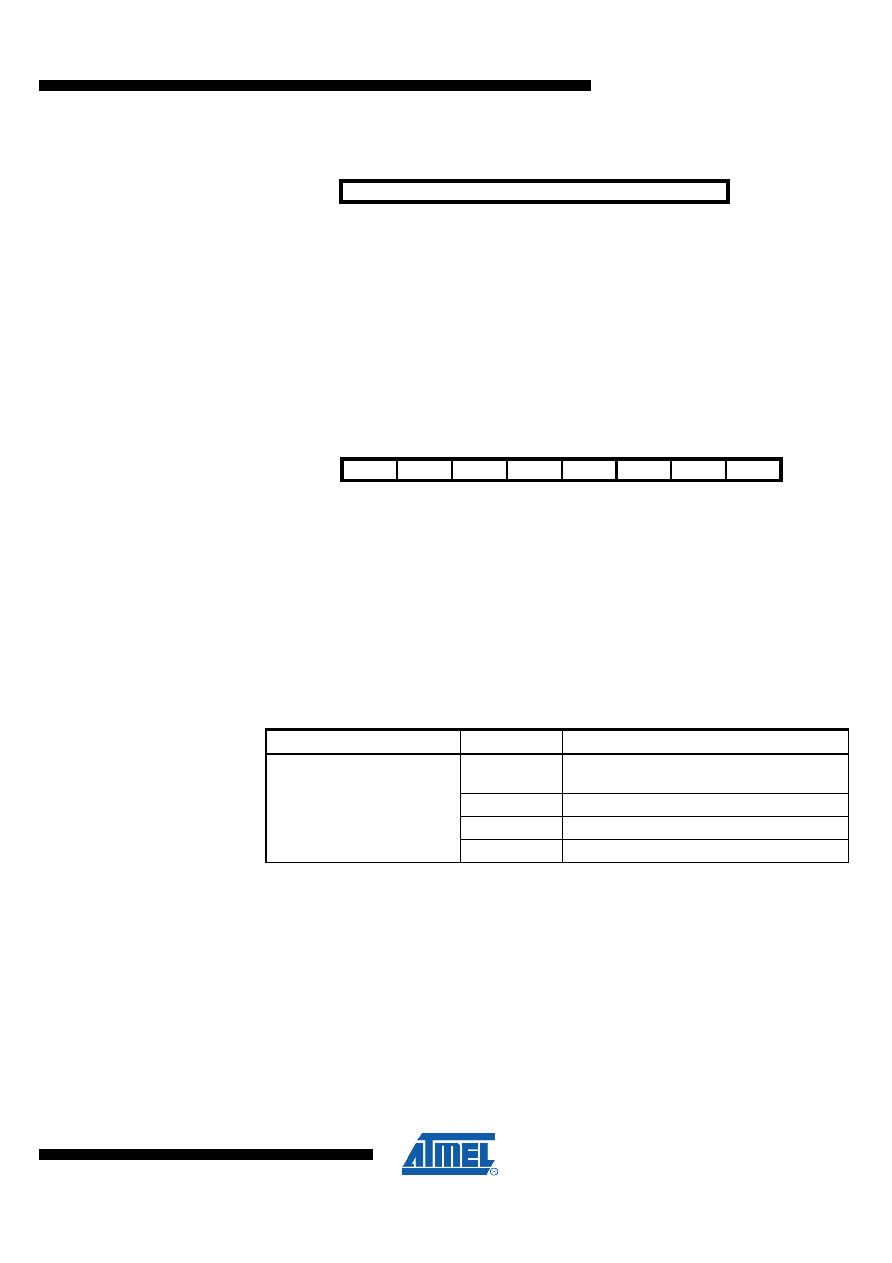

Table 8-4 EEPM Register Bits

Register Bits

Value

Description

0x00

Erase and Write in one operation (Atomic

Operation)

0x01

Erase only

0x02

Write only

EEPM1:0

0x03

Reserved for future use

Bit 3 – EERIE - EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interrupt if the I bit in SREG is set.

Writing EERIE to zero disables the interrupt. The EEPROM Ready interrupt generates a

constant interrupt when EEPE is cleared.

Bit 2 – EEMPE - EEPROM Master Write Enable

The EEMPE bit determines whether setting EEPE to one causes the EEPROM to be

written. When EEMPE is set, setting EEPE within four clock cycles will write data to the

EEPROM at the selected address If EEMPE is zero, setting EEPE will have no effect.

When EEMPE has been written to one by software, hardware clears the bit to zero after

four clock cycles. See the description of the EEPE bit for an EEPROM write procedure.

Bit 1 – EEPE - EEPROM Programming Enable

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC80C52CXXX-20/883D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-25SB | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52UXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| IS80C32U-S | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| IV80C52UXXX-S | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IT80F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|50V V(DRM)|8A I(T)RMS|TO-220 |

| IT80G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|50V V(DRM)|8A I(T)RMS|TO-220 |

| IT810B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| IT8152FG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Specification|Errata_v0.1 for it8152fg_v0.3.4 |

| IT8172G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RISC Companion Chip|Errata v0.2 for it8172g_v0.6 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。