- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄45383 > IT80C52EXXX-30SHXXX:R (TEMIC SEMICONDUCTORS) 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號(hào): | IT80C52EXXX-30SHXXX:R |

| 廠商: | TEMIC SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| 文件頁(yè)數(shù): | 13/60頁(yè) |

| 文件大?。?/td> | 5137K |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

20

8266D-MCU Wireless-06/12

ATmega128RFA1

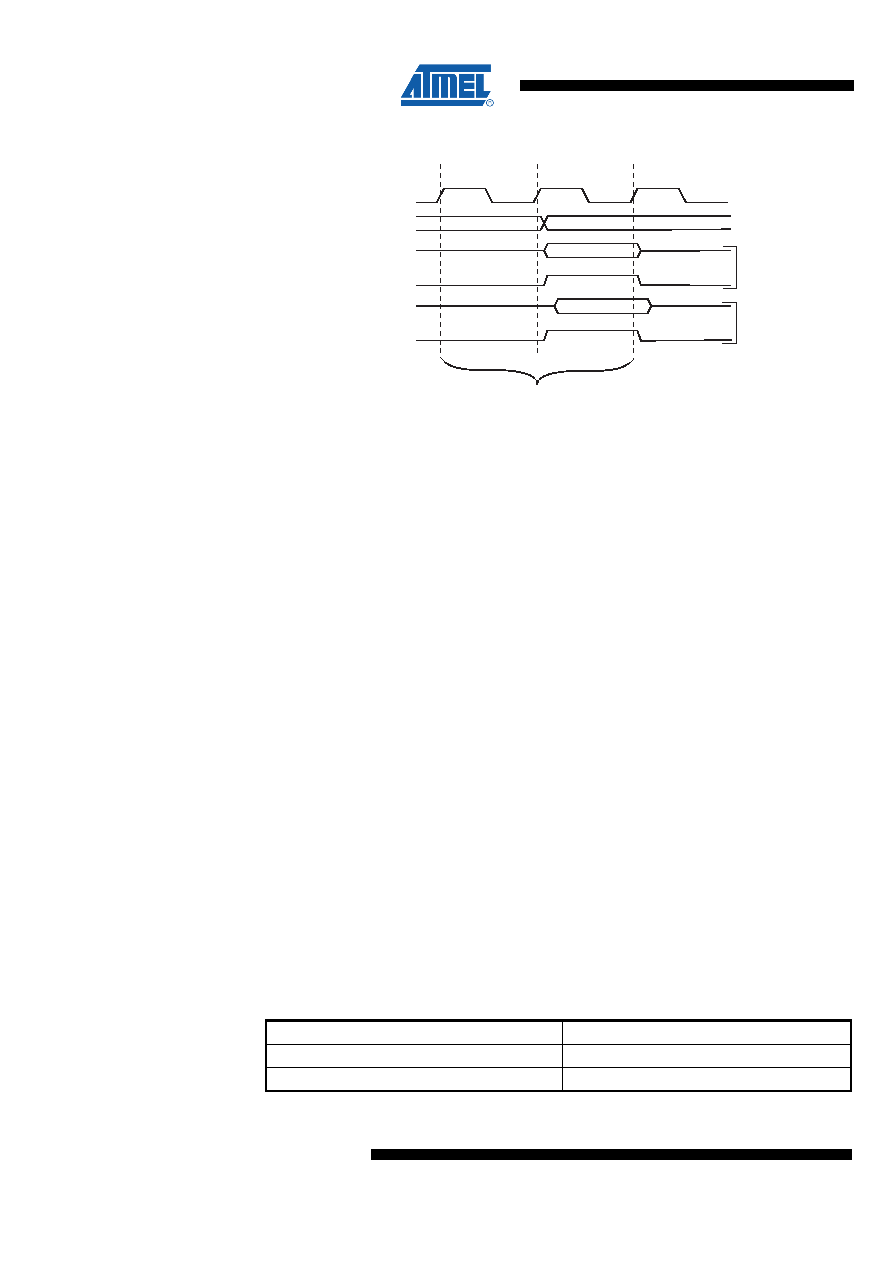

Figure 8-8. On-Chip Data SRAM Access Cycles

clk

WR

RD

Data

Address

Address valid

T1

T2

T3

Compute Address

Read

Wr

ite

CPU

Memory Access Instruction

Next Instruction

8.3 EEPROM Data Memory

The ATmega128RFA1 contains 4K Bytes of data EEPROM memory. It is organized as

a separate data space. Read access is byte-wise. The access between the EEPROM

and the CPU is described in the following, specifying the EEPROM Address Registers,

the EEPROM Data Register, and the EEPROM Control Register.

For a detailed description of SPI, JTAG and Parallel data downloading to the EEPROM,

486, and "Programming the EEPROM" on page 497 respectively.

8.3.1 EEPROM Read Write Access

The EEPROM Access Registers are accessible in the I/O space, see "EEPROM

The write access time for the EEPROM is given in Table 8-3 below. A self-timing

function, however, lets the user software detect when the next byte can be written. If the

user code contains instructions that write the EEPROM, some precautions must be

taken. In heavily filtered power supplies, DVDD is likely to rise or fall slowly on power-

up/down. This causes the device for some period of time to run at a voltage lower than

specified as minimum for the clock frequency used. See "Preventing EEPROM

Corruption" on page 24 for details on how to avoid problems in these situations.

In order to prevent unintentional EEPROM writes, a specific write procedure must be

followed. See the description of the EEPROM Control Register for details on this,

When the EEPROM is read, the CPU is halted for four clock cycles before the next

instruction is executed. When the EEPROM is written, the CPU is halted for two clock

cycles before the next instruction is executed.

The calibrated oscillator is used to time the EEPROM accesses. The following table

lists the typical programming time for EEPROM access from the CPU.

Table 8-3. EEPROM Programming Time

Symbol

Typical Programming time

EEPROM write (from CPU)

4.5 ms

EEPROM erase (from CPU)

8.5 ms

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MC80C52CXXX-20/883D | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, CDIP40 |

| MR80C52CXXX-25SB | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| MR80C52UXXX-25 | 8-BIT, MROM, 25 MHz, MICROCONTROLLER, CQCC44 |

| IS80C32U-S | 8-BIT, 20 MHz, MICROCONTROLLER, PQCC44 |

| IV80C52UXXX-S | 8-BIT, MROM, 20 MHz, MICROCONTROLLER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| IT80F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|50V V(DRM)|8A I(T)RMS|TO-220 |

| IT80G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TRIAC|50V V(DRM)|8A I(T)RMS|TO-220 |

| IT810B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| IT8152FG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Specification|Errata_v0.1 for it8152fg_v0.3.4 |

| IT8172G | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:RISC Companion Chip|Errata v0.2 for it8172g_v0.6 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。