- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384545 > ISPPAC-CLK5620V-01TN48C (Lattice Semiconductor Corporation) LED Area Light; LED Color:Red; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:630nm PDF資料下載

參數(shù)資料

| 型號(hào): | ISPPAC-CLK5620V-01TN48C |

| 廠商: | Lattice Semiconductor Corporation |

| 英文描述: | LED Area Light; LED Color:Red; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:630nm |

| 中文描述: | 在系統(tǒng)可編程,零延遲時(shí)鐘發(fā)生器通用扇出緩沖器 |

| 文件頁(yè)數(shù): | 30/47頁(yè) |

| 文件大?。?/td> | 871K |

| 代理商: | ISPPAC-CLK5620V-01TN48C |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)當(dāng)前第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

Lattice Semiconductor

ispClock5600 Family Data Sheet

30

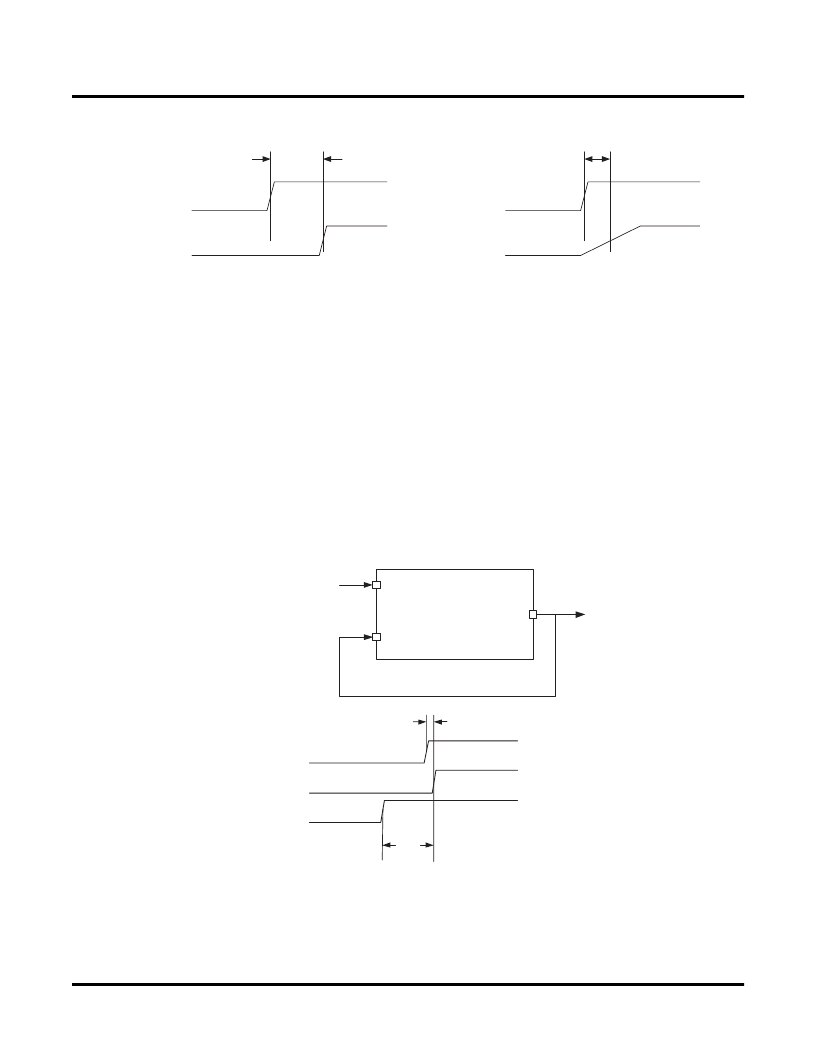

Figure 26. Output Timing Adders for Logic Type (a) and Output Slew Rate (b)

Similarly, when one changes the slew rate of an output, the output slew rate adders (t

IOS

) can be used to predict

the resulting skew. In this case, the fastest slew setting (1) is used as the baseline against which other slews are

measured. For example, in the case of outputs con

fi

gured to the same logic type (e.g. LVCMOS 1.8V), if one output

is set to the fastest slew rate (1, t

IOS

= 0ps), and another set to slew rate 3 (t

IOS

= 660ps), then one could expect

660ps of skew between the two outputs, as shown in Figure 26b.

Static Phase Offset and Input-Output Skew

The ispClock5600’s external feedback inputs can be used to obtain near-zero effective delays from the clock refer-

ence input pins to a designated output pin. In external feedback mode (Figure 27) the PLL will attempt to force the

output phase so that the rising edge phase (t

φ

) at the feedback input matches the rising edge phase at the refer-

ence input. The residual error between the two is speci

fi

ed as the static phase error. Note that any propagation

delays (t

FBK

) in the external feedback path drive the phase of the output signal

backwards

in time as measured at

the output. For this reason, if zero input-to-output delays are required in external feedback mode, the length of the

signal path between the output pin and the feedback pin should be minimized.

Figure 27. External Feedback Mode and Timing Relationships

Other Features

Internal Feedback Mode

In addition to supporting the use of external feedback to close the phase-locked loop, ispClock5620 also provides

the option of using an internal feedback path for this function. This feature is useful for minimizing external connec-

tions and routing in situations where one does not wish to attempt to compensate for external signal path delays.

LVPECL Output

(T

IOS

= 0)

LVTTL Output

(T

IOS

= 0.1ns)

0.15ns

(a)

LVCMOS Output

(Slew rate=1)

LVCMOS Output

(Slew rate=3)

660ps

(b)

Input Reference Clock

REF

FBK

BANK

OUTPUT

ispClock5600

Delay = t

FBK

t

φ

t

FBK

REF

FBK

BANK

OUTPUT

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPPAC-CLK5610V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:70mm; Forward Current:250mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:70x70mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA |

| ISPPAC-CLK5620V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:85mm; Forward Current:500mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:85x220mm; Peak Reflow Compatible (260 C):No |

| ISPPAC-POWR1014 | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ISPPAC-POWR1014-01T48I | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ISPPAC-POWR1014-01TN48I | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPPAC-CLK5620V-01TN48I | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-POWR1014 | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ISPPAC-POWR1014_08 | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ispPAC-POWR1014-01T48I | 功能描述:監(jiān)控電路 Prec. Prog. Pwr Sppl y Seq. Mon. Trim I RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類(lèi)型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開(kāi)關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

| ISPPAC-POWR1014-01TN148I | 制造商:Lattice Semiconductor Corporation 功能描述:#WR MGR ISP RESET & SEQ CNTRL 48TQFP |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。