- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄384545 > ISPPAC-CLK5620V-01TN100I (LATTICE SEMICONDUCTOR CORP) Backlight LED; Color:Infrared; Digit/Alpha Height:70mm; Forward Current:250mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:70x70mm; Peak Reflow Compatible (260 C):No PDF資料下載

參數(shù)資料

| 型號(hào): | ISPPAC-CLK5620V-01TN100I |

| 廠商: | LATTICE SEMICONDUCTOR CORP |

| 元件分類(lèi): | 時(shí)鐘及定時(shí) |

| 英文描述: | Backlight LED; Color:Infrared; Digit/Alpha Height:70mm; Forward Current:250mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:70x70mm; Peak Reflow Compatible (260 C):No |

| 中文描述: | 5600 SERIES, PLL BASED CLOCK DRIVER, 20 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PQFP100 |

| 封裝: | LEAD FREE, TQFP-100 |

| 文件頁(yè)數(shù): | 40/47頁(yè) |

| 文件大小: | 871K |

| 代理商: | ISPPAC-CLK5620V-01TN100I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)當(dāng)前第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

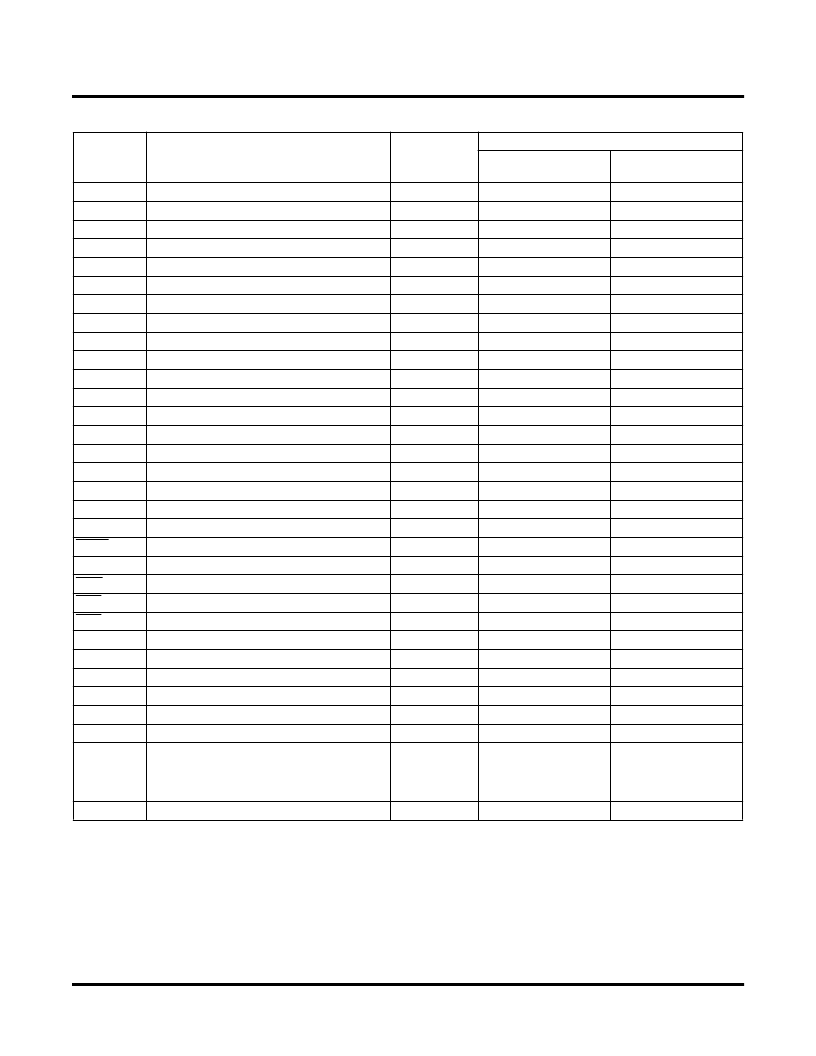

Lattice Semiconductor

ispClock5600 Family Data Sheet

40

VCCD

Digital Core VCC

Power

24, 33

47, 71

GNDD

Digital GND

GND

23, 48

46, 93

VCCJ

JTAG interface VCC

Power

36

74

REFA+

Clock Reference A positive input

Input

18

38

REFA-

Clock Reference A negative input

Input

19

39

REFB+

Clock Reference B positive input

Input

—

42

REFB-

Clock Reference B negative input

Input

Input

1

—

41

REFSEL

Clock Reference Select input (LVCMOS)

—

43

REFVTT

Termination voltage for reference inputs

Power

20

40

FBKA+

Clock feedback A positive input

Input

15

32

FBKA-

Clock feedback A negative input

Input

16

33

FBKB+

Clock feedback B positive input

Input

—

36

FBKB-

Clock feedback B negative input

Input

—

35

FBKSEL

Clock feedback select input (LVCMOS)

Input1

—

37

FBKVTT

Termination voltage for feedback inputs

Power

17

34

TDO

JTAG TDO Output line

Output

Input

2

35

73

TDI

JTAG TDI Input line

39

84

TCK

JTAG Clock Input

Input

Input

2

38

83

TMS

JTAG Mode Select

37

82

LOCK

PLL Lock indicator, LOW indicates PLL lock

Output

Input

1

Input

1

34

72

SGATE

Synchronous output gate

40

85

GOE

Global Output Enable

42

87

OEX

Output Enable 1

Input

21

44

OEY

Output Enable 2

Input

Input

1

Input

1

Input

1

Input

1

22

45

PS0

Pro

fi

le Select 0

44

89

PS1

Pro

fi

le Select 1

43

88

PLL_BYPASS PLL Bypass

47

92

RESET

Reset PLL

41

86

TEST1

Test Input 1 - connect to GNDD

Input

46

91

TEST2

Test Input 2 - connect to GNDD

Input

45

90

n/c

No internal connection

n/a

—

1, 2, 23, 24, 25, 26, 27,

28, 29, 48, 49, 50, 75,

76, 77, 78, 79, 94, 97,

98, 99, 100

Reserved

Factory use only - Do not connect

n/a

—

80, 81, 95, 96

1. Internal pull-down resistor.

2. Internal pull-up resistor.

Pin Descriptions (Continued)

Pin Name

Description

Pin Type

Pin Number

ispClock5610

48 TQFP

ispClock5620

100 TQFP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ISPPAC-CLK5610V-01TN48C | LED Ring Light; LED Color:Infrared; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No; Supply Current:350mA; Supply Voltage:24VDC; Wavelength:880nm |

| ISPPAC-CLK5620V-01TN48C | LED Area Light; LED Color:Red; Leaded Process Compatible:No; Light Emitting Area:62x62mm; Peak Reflow Compatible (260 C):No; Supply Current:200mA; Supply Voltage:24VDC; Wavelength:630nm |

| ISPPAC-CLK5610V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:70mm; Forward Current:250mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:70x70mm; Peak Reflow Compatible (260 C):No; Supply Current:250mA |

| ISPPAC-CLK5620V-01TN48I | Backlight LED; Color:Red; Digit/Alpha Height:85mm; Forward Current:500mA; Operating Temperature Range:0 C to +50 C; Leaded Process Compatible:No; Light Emitting Area:85x220mm; Peak Reflow Compatible (260 C):No |

| ISPPAC-POWR1014 | In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ISPPAC-CLK5620V-01TN48C | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-CLK5620V-01TN48I | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable, Zero-Delay Clock Generator with Universal Fan-Out Buffer |

| ISPPAC-POWR1014 | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ISPPAC-POWR1014_08 | 制造商:LATTICE 制造商全稱(chēng):Lattice Semiconductor 功能描述:In-System Programmable Power Supply Supervisor, Reset Generator and Sequencing Controller |

| ispPAC-POWR1014-01T48I | 功能描述:監(jiān)控電路 Prec. Prog. Pwr Sppl y Seq. Mon. Trim I RoHS:否 制造商:STMicroelectronics 監(jiān)測(cè)電壓數(shù): 監(jiān)測(cè)電壓: 欠電壓閾值: 過(guò)電壓閾值: 輸出類(lèi)型:Active Low, Open Drain 人工復(fù)位:Resettable 監(jiān)視器:No Watchdog 電池備用開(kāi)關(guān):No Backup 上電復(fù)位延遲(典型值):10 s 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:UDFN-6 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。