- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄385408 > HT95C30P (Holtek Semiconductor Inc.) 8-Bit CID Type Phone Controller MCU PDF資料下載

參數(shù)資料

| 型號: | HT95C30P |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | 8-Bit CID Type Phone Controller MCU |

| 中文描述: | 8位偵緝型電話MCU控制器 |

| 文件頁數(shù): | 17/50頁 |

| 文件大小: | 324K |

| 代理商: | HT95C30P |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁當前第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

HT95C200/20P/300/30P

Rev. 0.10

17

October 1, 2002

Preliminary

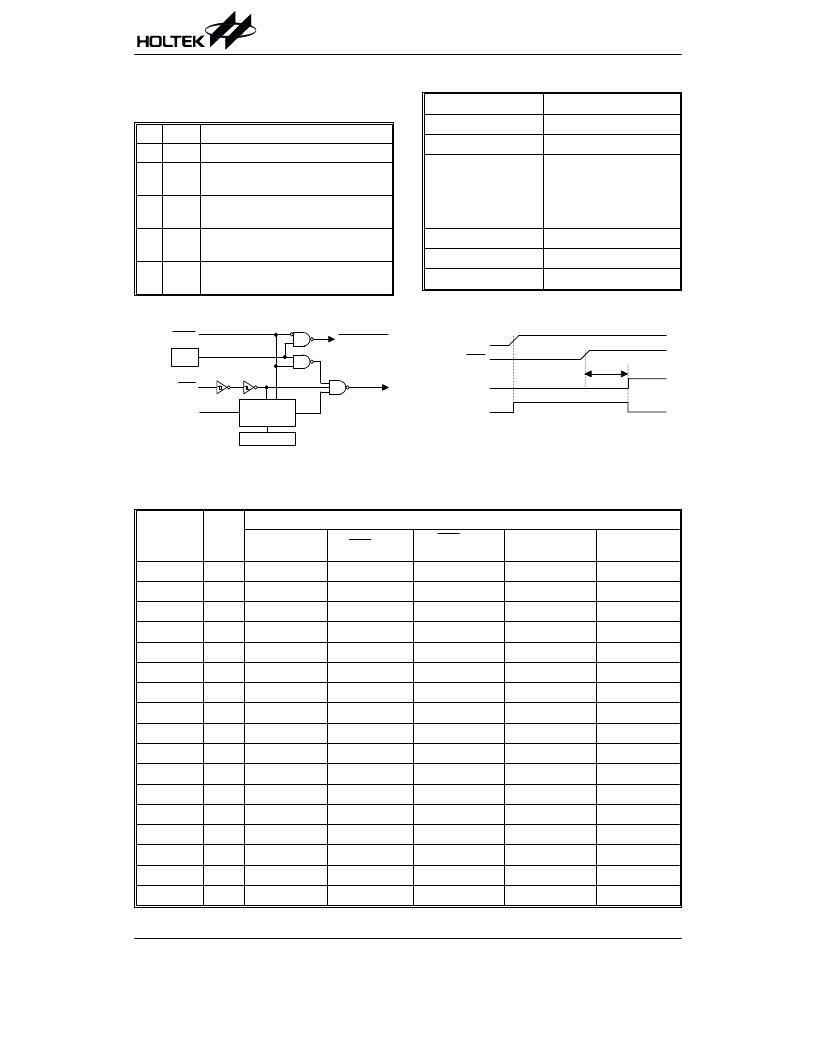

By examining the processor status flags PD and TO, the

software program can distinguish between the different

chip resets .

TO

PD

Reset Condition

0

0

Power on reset

u

u

External reset during Normal mode or

Green mode

0

1

External reset during Sleep mode or

Idle mode

1

u

WDT time-out during Normal mode or

Green mode

1

1

WDT time-out during Sleep mode or

Idle mode

Note: u means unchanged

The functional units chip reset status are shown below:

Program Counter

000H

Interrupt

Disabled

Prescaler

Cleared

WDT

Cleared

After a master reset, WDT

begins counting.

(If WDT function is enabled

by mask option)

Timer/EventCounter0/1 Off

Input/output Port

Input mode

Stack Pointer

Pointstothetopofthestack

7

"

7

8 "

5

D

1

' A C

"

8

7

"

A

; @

8 " " "

;

"

Reset configuration

;

>

"

A

" "

Reset timing chart

When the reset conditions occurred, some registers may be changed or unchanged.

Register

Addr.

Reset Conditions

Power On

RES Pin

RES Pin

(Sleep/Idle)

WDT

WDT

(Sleep/Idle)

IAR0

00H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

MP0

01H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

IAR1

02H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

MP1

03H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

BP

04H

---0 0000

---0 0000

---0 0000

---0 0000

---u uuuu

ACC

05H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

PCL

06H

0000H

0000H

0000H

0000H

0000H

TBLP

07H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TBLH

08H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

WDTS

09H

0000 0111

0000 0111

0000 0111

0000 0111

uuuu uuuu

STATUS

0AH

--00 xxxx

--uu uuuu

--01 uuuu

--1u uuuu

--11 uuuu

INTC0

0BH

-000 0000

-000 0000

-000 0000

-000 0000

uuuu uuuu

TMR0H

0CH

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TMR0L

0DH

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TMR0C

0EH

00-0 1---

00-0 1---

00-0 1---

00-0 1---

uu-u u---

TMR1H

0FH

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TMR1L

10H

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

相關PDF資料 |

PDF描述 |

|---|---|

| HT95C200 | 8-Bit CID Type Phone Controller MCU |

| HT95CXXX | CID Type Phone 8-Bit MCU |

| HT95L400-128QFP-A | LCD Type Phone 8-Bit MCU |

| HT95L100-64QEP-A | LCD Type Phone 8-Bit MCU |

| HT95L10P-64QEP-A | LCD Type Phone 8-Bit MCU |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| HT95C400 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95C40P | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

| HT95CXXX | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95L000 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:CID Type Phone 8-Bit MCU |

| HT95L000-56SSOP-A | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:LCD Type Phone 8-Bit MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復。