- 您現(xiàn)在的位置:買(mǎi)賣IC網(wǎng) > PDF目錄385404 > HT82M9BAE (Holtek Semiconductor Inc.) USB Mouse Encoder 8-Bit MCU with EEPROM PDF資料下載

參數(shù)資料

| 型號(hào): | HT82M9BAE |

| 廠商: | Holtek Semiconductor Inc. |

| 英文描述: | USB Mouse Encoder 8-Bit MCU with EEPROM |

| 中文描述: | USB鼠標(biāo)編碼器8位微控制器帶有EEPROM |

| 文件頁(yè)數(shù): | 13/47頁(yè) |

| 文件大小: | 336K |

| 代理商: | HT82M9BAE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)當(dāng)前第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)

HT82M9BEE/HT82M9BAE

Rev. 1.20

13

August 13, 2007

TO PDF

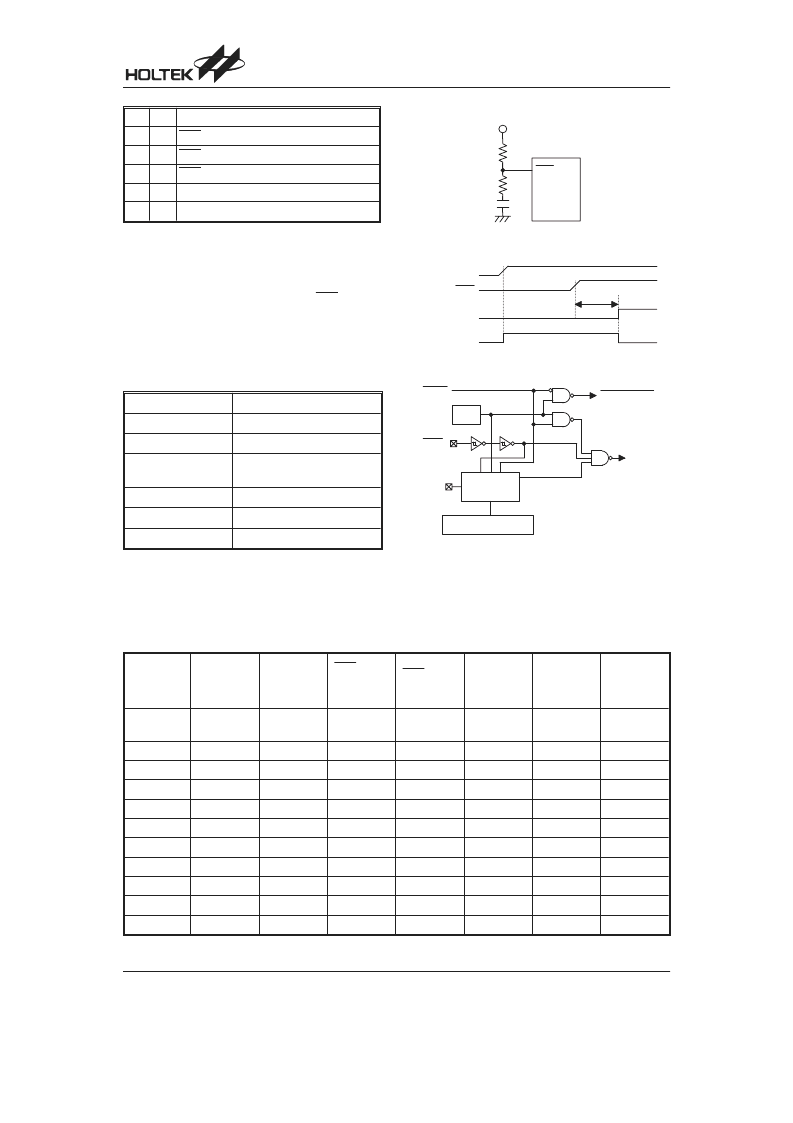

RESET Conditions

0

0

RES reset during power-up

u

u

RES reset during normal operation

0

1

RES wake-up HALT

1

u

WDT time-out during normal operation

1

1

WDT wake-up HALT

Note: u stands for unchanged

To guarantee that the system oscillator is started and

stabilized, the SST (System Start-up Timer) provides an

extra delay of 1024 system clock pulses when the sys-

tem resets (power-up, WDT time-out or RES reset) or

the system awakes from the HALT state.

When a system reset occurs, the SST delay is added

during the reset period. Any wake-up from HALT will en-

able the SST delay.

The functional unit chip reset status are shown below.

Program Counter

000H

Interrupt

Disable

Prescaler

Clear

WDT

Clear. After master reset,

WDT begins counting

Timer/event Counter

Off

Input/output Ports

Input mode

Stack Pointer

Points to the top of the stack

Reset Circuit

/

-

/

=

"

0 !

-

1 *

-

0

Reset Configuration

-

*

#

- -

Reset Timing Chart

The registers status are summarized in the following table.

Register

Reset

(Power On)

WDT

Time-out

(Normal

Operation)

RES Reset

(Normal

Operation)

RES Reset

(HALT)

WDT

Time-out

(HALT)*

USB Reset

(Normal)

USB Reset

(HALT)

Program

Counter

000H

000H

000H

000H

000H

000H

000H

MP0

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

MP1

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

BP

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

0000 0000

ACC

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TBLP

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

TBLH

xxxx xxxx

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

uuuu uuuu

WDTS

1000 0111

1000 0111

1000 0111

1000 0111

uuuu uuuu

1000 0111

1000 0111

STATUS

--00 xxxx

--1u uuuu

--00 uuuu

--00 uuuu

--11 uuuu

--uu uuuu

--01 uuuu

INTC

-000 0000

-000 0000

-000 0000

-000 0000

-uuu uuuu

-000 0000

-000 0000

TMR0

xxxx xxxx

0000 0000

0000 0000

0000 0000

uuuu uuuu

uuuu uuuu

uuuu uuuu

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HT82M9BEE | USB Mouse Encoder 8-Bit MCU with EEPROM |

| HT82P604B | DC-DC Converter |

| HT82V14 | 14-Bit CCD/CIS Analog Signal Processor(14位CCD/CIS模擬信號(hào)處理器) |

| HT82V16 | 16-Bit CCD/CIS Analog Signal Processor(16位CCD/CIS模擬信號(hào)處理器) |

| HT82V24 | 16-Bit, 15MSPS, 3-Channel CCD/CIS Analog Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HT82M9BEE | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:USB Mouse Encoder 8-Bit MCU with EEPROM |

| HT82P4352-16SOP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| HT82P604B | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:DC-DC Converter |

| HT82T20-20SOP | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Logic IC |

| HT82V14 | 制造商:HOLTEK 制造商全稱:Holtek Semiconductor Inc 功能描述:14-Bit CCD/CIS Analog Signal Processor |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。