- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384423 > HIP7030A2P (HARRIS SEMICONDUCTOR) FPGA - 200000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN PDF資料下載

參數(shù)資料

| 型號(hào): | HIP7030A2P |

| 廠商: | HARRIS SEMICONDUCTOR |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | FPGA - 200000 SYSTEM GATE 2.5 VOLT - NOT RECOMMENDED for NEW DESIGN |

| 中文描述: | 8-BIT, MROM, 5 MHz, MICROCONTROLLER, PDIP28 |

| 文件頁數(shù): | 4/10頁 |

| 文件大小: | 44K |

| 代理商: | HIP7030A2P |

9-43

Specifications HIP7030A0

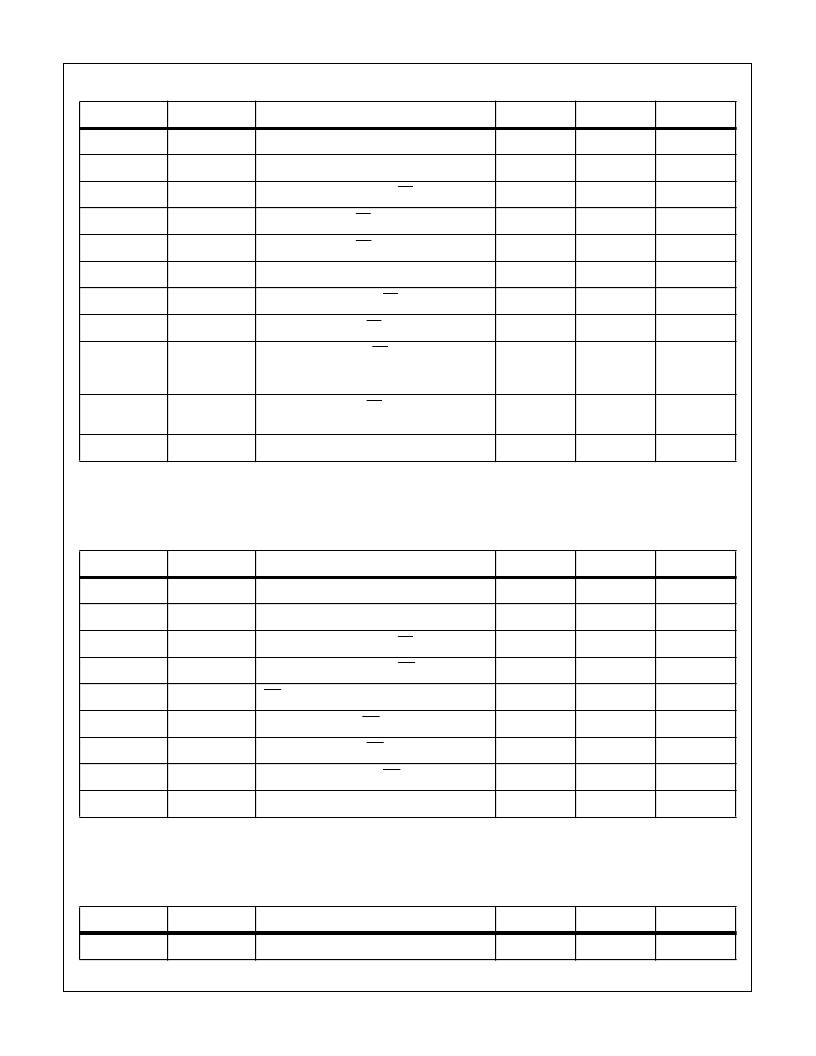

Read Cycle Timing

(ALC = 0) (See Figure 1) V

DD

= 5V

DC

±

10%, V

SS

= 0V

DC

, T

A

= -40

o

C to +125

o

C Unless Otherwise Specified.

NUMBER

SYMBOL

PARAMETER

MIN

MAX

UNITS

f

OSC

OSCB Operating Frequency

1

10

MHz

(1)

t

CYC

Read Cycle Time

200

2000

ns

(2)

t

AVCEL

Address Setup Time Before CE

-10

-

ns

(3)

t

DVCEL

Access Time From CE

-

t

CYC

- 80

ns

(4)

t

DVRDL

Access Time From RD

-

0.75t

CYC

- 80

ns

(5)

t

DVAV

Access Time From Address Change

-

t

CYC

- 80

ns

(6)

t

CEHAX

Address Hold Time After CE

0

-

ns

(7)

t

CEHAX

Data Hold Time After CE

0

-

ns

(8)

t

RDLDX

Data Bus Driven From RD

(Time to Data Active from High Impedance

State)

0

-

ns

(9)

t

RDHAX

Data Hold Time After RD

(Hold Time to High Impedance State)

0

-

ns

(10)

t

OSCDS

OSCB to DS Propagation Delay

5

25

ns

NOTE:

Minimum frequency applies when ALC is low.

Write Cycle Timing

(ALC = 0) (See Figure 2) V

DD

= 5V

DC

±

10%, V

SS

= 0V

DC

, T

A

= -40

o

C to +125

o

C Unless Otherwise Specified.

NUMBER

SYMBOL

PARAMETER

MIN

MAX

UNITS

f

OSC

OSCB Operating Frequency

1

10

MHz

(1)

t

CYC

Write Cycle Time

200

2000

ns

(2)

t

AVCEL

Address Setup Time Before CE

-10

-

ns

(3)

t

AVWEL

Address Setup Time Before WE

0.25t

CYC

- 25

-

-

(4)

t

WEWE

WE Pulse Width

0.5t

CYC

- 10

-

ns

(5)

t

DVWEH

Data Set-up Time to WE Trailing Edge

0.75t

CYC

- 75

-

ns

(6)

t

WEHDX

Data Hold Time After WE Trailing Edge

0.25t

CYC

- 20

-

ns

(7)

t

WEHAX

Address Hold Time After WE Trailing Edge

0.25t

CYC

- 20

-

ns

(8)

t

OSCDS

OSCB to DS Propagation Delay

5

25

ns

NOTE:

1. Minimum frequency applies when ALC is low.

Read Cycle Timing (ALC = 1)

(See Figure 3) V

DD

= 5V

DC

±

10%, V

SS

= 0V

DC

, T

A

= -40

o

C to +125

o

C Unless Otherwise Specified.

NUMBER

SYMBOL

PARAMETER

MIN

MAX

UNITS

f

OSC

OSCB Operating Frequency

10

MHz

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| HIP9010 | Engine Knock Signal Processor |

| HIP9010AB | Engine Knock Signal Processor |

| HIP9011ABZ | Engine Knock Signal Processor |

| HIP9011 | Engine Knock Signal Processor |

| HIP9011AB | Engine Knock Signal Processor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| HIP7030PD WAF | 制造商:Harris Corporation 功能描述: |

| HIP7038A8 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:J1850 8-Bit 68HC05 Microcontroller 8K EEPROM Version |

| HIP7038A8F | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:J1850 8-Bit 68HC05 Microcontroller 8K EEPROM Version |

| HIP8112A | 制造商:HARRIS 制造商全稱:HARRIS 功能描述:NTSC/PAL Video Decoder |

| HIP-8V | 制造商:Belden Inc 功能描述:SPLITTER 8 WAY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。