- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375853 > FM8P51EP (Electronic Theatre Controls, Inc.) EPROM/ROM-Based 8-Bit Microcontroller PDF資料下載

參數(shù)資料

| 型號(hào): | FM8P51EP |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | EPROM/ROM-Based 8-Bit Microcontroller |

| 中文描述: | 存儲(chǔ)器/基于ROM的8位微控制器 |

| 文件頁(yè)數(shù): | 23/60頁(yè) |

| 文件大小: | 369K |

| 代理商: | FM8P51EP |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)當(dāng)前第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)

FM8P51

Rev1.2 Mar 15, 2005

P.23/FM8P51

FEELING

TECHNOLOGY

prescaler with a division ratio of up to 1:128 can be assigned to the WDT controlled by the OPTION register. Thus,

the longest time-out period is approxmately 2.3 seconds if reset delay time is set to 18ms.

The CLRWDT instruction clears the WDT and the prescaler, if assigned to the WDT, and prevents it from timing out

and generating a device reset.

The SLEEP instruction resets the WDT and the prescaler, if assigned to the WDT. This gives the maximum SLEEP

time before a WDT Wake-up Reset.

2.3.3 Prescaler

An 8-bit counter (down counter) is available as a prescaler for the Timer0, or as a postscaler for the Watchdog Timer

(WDT). Note that the prescaler may be used by either the Timer0 module or the WDT, but not both. Thus, a

prescaler assignment for the Timer0 means that there is no prescaler for the WDT, and vice-versa.

The PSA bit (OPTION<3>) determines prescaler assignment. The PS<2:0> bits (OPTION<2:0>) determine

prescaler ratio.

When the prescaler is assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the

prescaler. When it is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

The prescaler is neither readable nor writable. On a RESET, the prescaler contains all ‘1’s.

To avoid an unintended device reset, CLRWDT or CLRR TMR0 instructions must be executed when changing the

prescaler assignment from Timer0 to the WDT, and vice-versa.

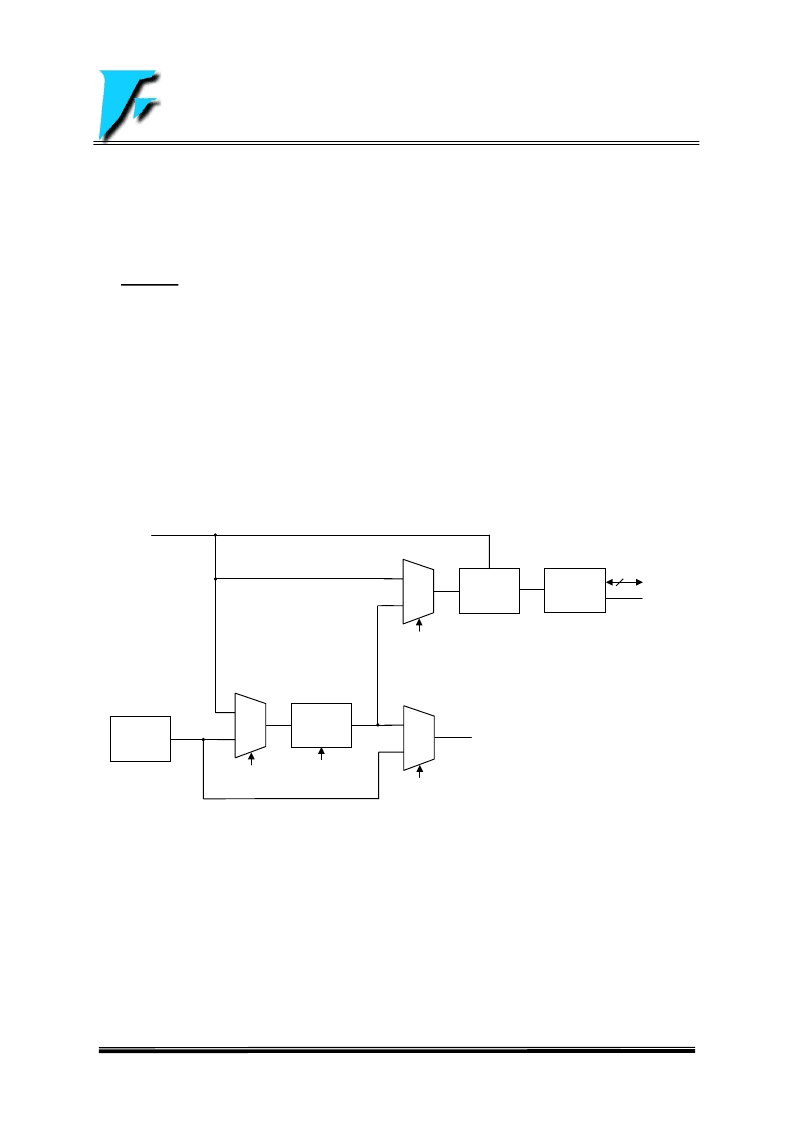

FIGURE 2.4: Block Diagram of The Timer0/WDT Prescaler

2.4 Timer1

The Timer1 is a 8-bit clock counter with a programmable prescaler and a 8-bit period register (PR1). It also can be

as a baud rate clock generator for the SPI module. The clock source of Timer1 comes from the internal clock

(Fosc/4). The option of Timer1 prescaler (1:1, 1:4, 1:8, 1:16) is defined by T1P1:T1P0 (T1CON<1:0>) bits.

The

prescaler is cleared when a value is written to TMR1 or T1CON register, and during any kind of reset as

well.

The timer increments from 00h until it equals the period register (PR1). It then resets to 00h at the next increment

cycle. The timer interrupt flag (T1IF) is set when the timer rollover to 00h.

The timer also has a corresponding interrupt enable bit (T1IE). The timer interrupt can be enabled/disabled by

setting/clearing this bit.

The timer s can be turned on and off under software control. When the timer on control bit (T1ON, T1CON<2>) is set,

the timer increments from the clock source. When T1ON is cleared, the timer is turned off and cannot cause the

MUX

0

1

Watchdog

Timer

PSA

8-Bit

Prescaler

PS2:PS0

WDT Time-out

MUX

1

0

PSA

MUX

1

0

PSA

Sync

2 Cycles

Instruction Cycle

(Fosc/4 or Fosc/2)

TMR0

Register

Data Bus

8

Set T0IF flag

on overflow

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FM8P51F | EPROM/ROM-Based 8-Bit Microcontroller |

| FM8P51P | EPROM/ROM-Based 8-Bit Microcontroller |

| FM8P51E | EPROM/ROM-Based 8-Bit Microcontroller |

| FM8P54 | EPROM/ROM-Based 8-Bit Microcontroller Series |

| FM8P54E | EPROM/ROM-Based 8-Bit Microcontroller Series |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FM8P51F | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller |

| FM8P51P | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller |

| FM8P54 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

| FM8P54E | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

| FM8P56 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EPROM/ROM-Based 8-Bit Microcontroller Series |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。