- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375760 > FC80960HA40SL2GW (INTEL CORP) CAP CER 3300PF 250V 10% X7R 0805 PDF資料下載

參數(shù)資料

| 型號: | FC80960HA40SL2GW |

| 廠商: | INTEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | CAP CER 3300PF 250V 10% X7R 0805 |

| 中文描述: | 32-BIT, 40 MHz, RISC PROCESSOR, PQFP208 |

| 封裝: | PLASTIC, QFP-208 |

| 文件頁數(shù): | 42/102頁 |

| 文件大?。?/td> | 828K |

| 代理商: | FC80960HA40SL2GW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁當(dāng)前第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁

80960HA/HD/HT

36

Advance Information

Datasheet

Table 23. AC Characteristics Notes

NOTES:

1. See

Section 4.8, “AC Timing Waveforms” on page 38

for waveforms and definitions.

2. See

Figure 25 “Output Delay or Hold vs. Load Capacitance” on page 44

for capacitive derating information

for output delays and hold times.

3. See

Figure 22 “Rise and Fall Time Derating at 85°C and Minimum V

CC

” on page 43

for capacitive derating

information for rise and fall times.

4. Where N is the number of N

RAD

, N

RDD

, N

WAD

or N

WDD

wait states that are programmed in the Bus

Controller Region Table. WAIT never goes active when there are no wait states in an access.

5. N = Number of wait states inserted with READY.

6. These specifications are guaranteed by the processor.

7. These specifications must be met by the system for proper operation of the processor.

8. RESET is an asynchronous input that has no required setup and hold time for proper operation. However,

to guarantee the device exits the reset mode synchronized to a particular clock edge, the rising edge of

RESET must meet setup and hold times to the rising edge of the CLKIN.

9. The interrupt pins are synchronized internally by the 80960Hx. They have no required setup or hold times

for proper operation. These pins are sampled by the interrupt controller every clock and must be active for

at least two consecutive CLKIN rising edges when asserting them asynchronously. To guarantee

recognition at a particular clock edge, the setup and hold times shown must be met.

10.Relative Output timings are not tested.

11.Not tested.

12.The processor minimizes changes to the bus signals when transitioning from a bus cycle to an idle bus for

the following signals: A31:4, SUP, CT3:0, D/C, LOCK, W/R, BE3:0.

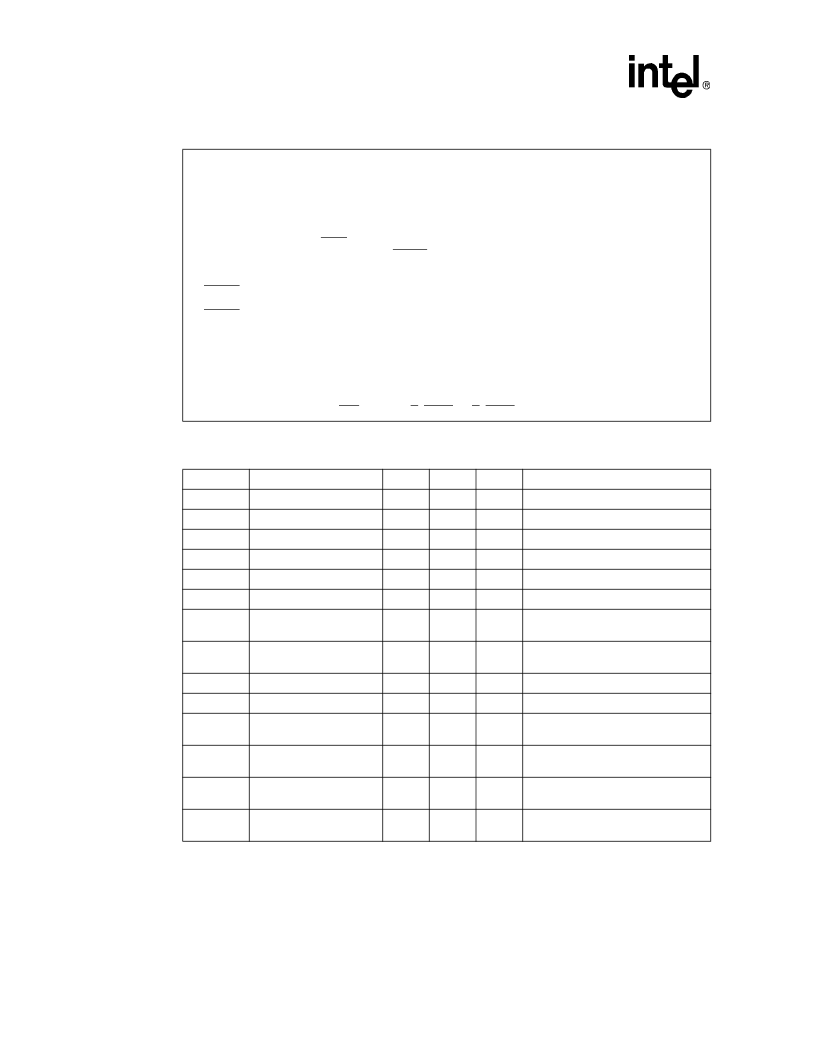

Table 24. 80960Hx Boundary Scan Test Signal Timings

Symbol

Parameter

Min

Max

Units

Notes

T

BSF

TCK Frequency

0

8

MHz

T

BSC

TCK Period

125

Infinite

ns

T

BSCH

TCK High Time

40

ns

Measured at 1.5 V (1)

T

BSCL

TCK Low Time

40

ns

Measured at 1.5 V (1)

T

BSCR

TCK Rise Time

8

ns

0.8 V to 2.0 V (1)

T

BSCF

TCK Fall Time

8

ns

2.0 V to 0.8 V (1)

T

BSIS1

Input Setup to TCK —

TDI, TMS

8

ns

T

BSIH1

Input Hold from TCK —

TDI, TMS

10

ns

T

BSOV1

TDO Valid Delay

3

30

ns

T

BSOF1

TDO Float Delay

36

ns

(1)

T

BSOV2

All Outputs (Non-Test)

Valid Delay

3

30

ns

Relative to TCK

T

BSOF2

All Outputs (Non-Test)

Float Delay

36

ns

Relative to TCK (1)

T

BSIS2

Input Setup to TCK - All

Inputs (Non-Test)

8

ns

T

BSIH2

Input Hold from TCK - All

Inputs (Non-Test)

10

ns

NOTE:

1. Not tested.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FC80960HA33SL2GV | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HD32SL2GL | 80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FCA-125 | Tyco Electronics Mid-Range Military/Aerospace Relays |

| FCA16N60 | 600V N-Channel MOSFET |

| FCA20N60 | 600V N-Channel MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| FC80960HD32SL2GL | 功能描述:IC MPU I960HD 3V 32MHZ 208-QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:60 系列:SCC 處理器類型:Z380 特點(diǎn):全靜電 Z380 CPU 速度:20MHz 電壓:5V 安裝類型:表面貼裝 封裝/外殼:144-LQFP 供應(yīng)商設(shè)備封裝:144-LQFP 包裝:托盤 |

| FC80960HD50SL2GM | 制造商:INTEL 制造商全稱:Intel Corporation 功能描述:80960HA/HD/HT 32-Bit High-Performance Superscalar Processor |

| FC80960HD66SL2GN | 功能描述:IC MPU I960HD 3V 66MHZ 208-SQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:2 系列:MPC8xx 處理器類型:32-位 MPC8xx PowerQUICC 特點(diǎn):- 速度:133MHz 電壓:3.3V 安裝類型:表面貼裝 封裝/外殼:357-BBGA 供應(yīng)商設(shè)備封裝:357-PBGA(25x25) 包裝:托盤 |

| FC80960HD80 | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| FC80960HD80SL2LZ | 功能描述:IC I960HD 3.3V 80MHZ 208QFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - 微處理器 系列:- 標(biāo)準(zhǔn)包裝:40 系列:MPC83xx 處理器類型:32-位 MPC83xx PowerQUICC II Pro 特點(diǎn):- 速度:267MHz 電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 封裝/外殼:516-BBGA 裸露焊盤 供應(yīng)商設(shè)備封裝:516-PBGAPGE(27x27) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。