- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384281 > EDS1232AASE-75-E (ELPIDA MEMORY INC) ER 6C 3#16 3#8 SKT RECP PDF資料下載

參數(shù)資料

| 型號: | EDS1232AASE-75-E |

| 廠商: | ELPIDA MEMORY INC |

| 元件分類: | DRAM |

| 英文描述: | ER 6C 3#16 3#8 SKT RECP |

| 中文描述: | 4M X 32 SYNCHRONOUS DRAM, 5.4 ns, PBGA90 |

| 封裝: | ROHS COMPLIANT, FBGA-90 |

| 文件頁數(shù): | 49/55頁 |

| 文件大?。?/td> | 564K |

| 代理商: | EDS1232AASE-75-E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁當前第49頁第50頁第51頁第52頁第53頁第54頁第55頁

EDS1232CABB, EDS1232CATA

Preliminary Data Sheet E0247E40 (Ver. 4.0)

49

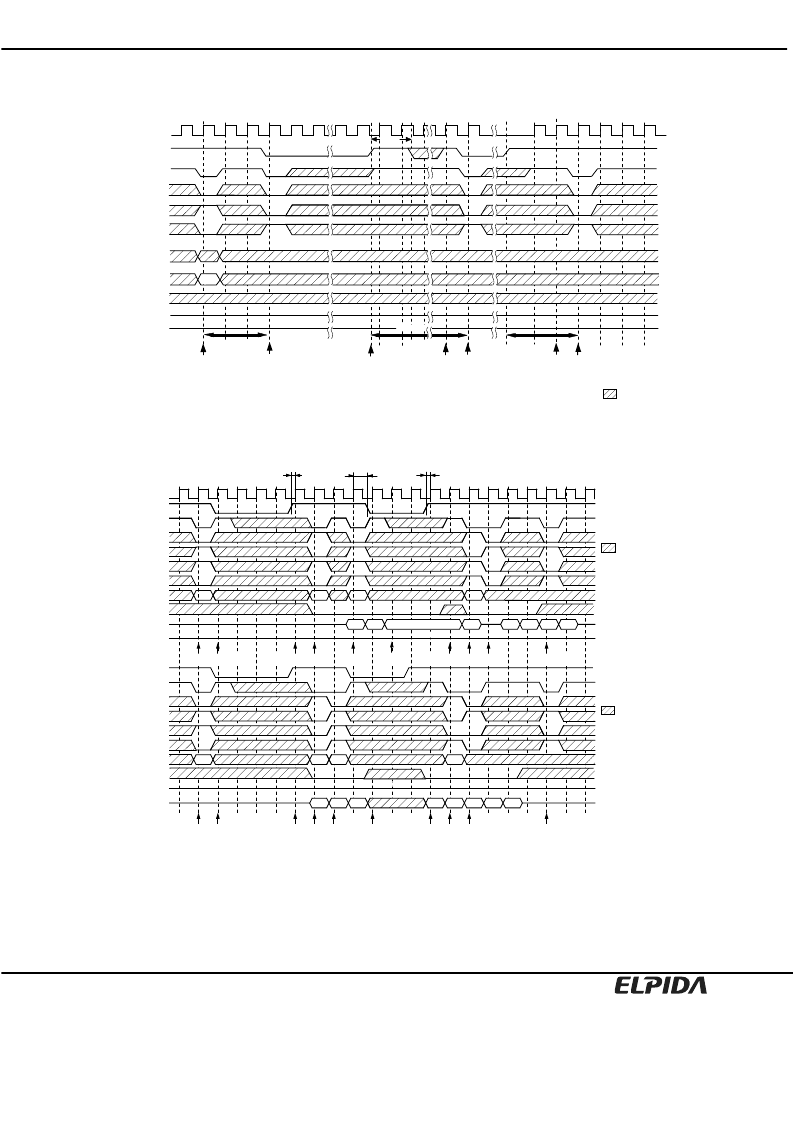

Self Refresh Cycle

CLK

CKE

/CS

/RAS

/CAS

/WE

BS

Address

DQM

DQ (input)

DQ (output)

Precharge command

Self refresh entry

Auto

Self refresh exit

CKE Low

A10=1

RC

t

RP

t

Self refresh cycle

/RAS-/CAS delay = 3

CL = 3

BL = 4

=

VIH or VIL

High-Z

Next

RC

t

Next

lSREX

Self refresh entry

Clock Suspend Mode

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

R:a

C:a

R:b

a

a+1 a+2

a+3

b

b+1 b+2

R:a

C:a R:b

C:b

a

a+1 a+2

b

b+1 b+2 b+3

C:b

Bank0

Active clock

Active clock

Bank0

Bank3

Reastart

Read suspend

Bank0

Bank3

Earliest Bank3

Bank0

Bank0

Active clock

Active clock

Bank3

Writstart

Write suspend

Bank3

Bank0

Earliest Bank3

b+3

CKE

/RAS

/CS

/CAS

/WE

Address

DQM

CLK

BS

CKE

/RAS

/CS

/CAS

/WE

BS

Address

DQM

a+3

High-Z

High-Z

tHI

tSI

tSI

Read cycle

/RAS-/CAS delay = 2

/CAS latency = 2

Burst length = 4

= VIH or VIL

Write cycle

/RAS-/CAS delay = 2

/CAS latency = 2

Burst length = 4

= VIH or VIL

DQ (output)

DQ (input)

DQ (output)

DQ (input)

相關PDF資料 |

PDF描述 |

|---|---|

| EDS1232AASE-75L-E | ER 2C 2#8 SKT RECP LINE |

| EDS1232CABB-1AL-E | 128M bits SDRAM |

| EDS1232AABB-75L-E | 128M bits SDRAM |

| EDS1232CABB-75L-E | 128M bits SDRAM |

| EDS1232AATA-75L-E | 128M bits SDRAM (4M words x 32 bits) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| EDS1232AASE-75L-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M bits SDRAM (4M words x 32 bits) |

| EDS1232AATA | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M bits SDRAM |

| EDS1232AATA-60 | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M bits SDRAM (4M words x 32 bits) |

| EDS1232AATA-60-E | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M bits SDRAM (4M words x 32 bits) |

| EDS1232AATA-60L | 制造商:ELPIDA 制造商全稱:Elpida Memory 功能描述:128M bits SDRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。