- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376630 > DDX4100A PDF資料下載

參數(shù)資料

| 型號(hào): | DDX4100A |

| 文件頁數(shù): | 24/27頁 |

| 文件大?。?/td> | 1737K |

| 代理商: | DDX4100A |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁

DDX-4100

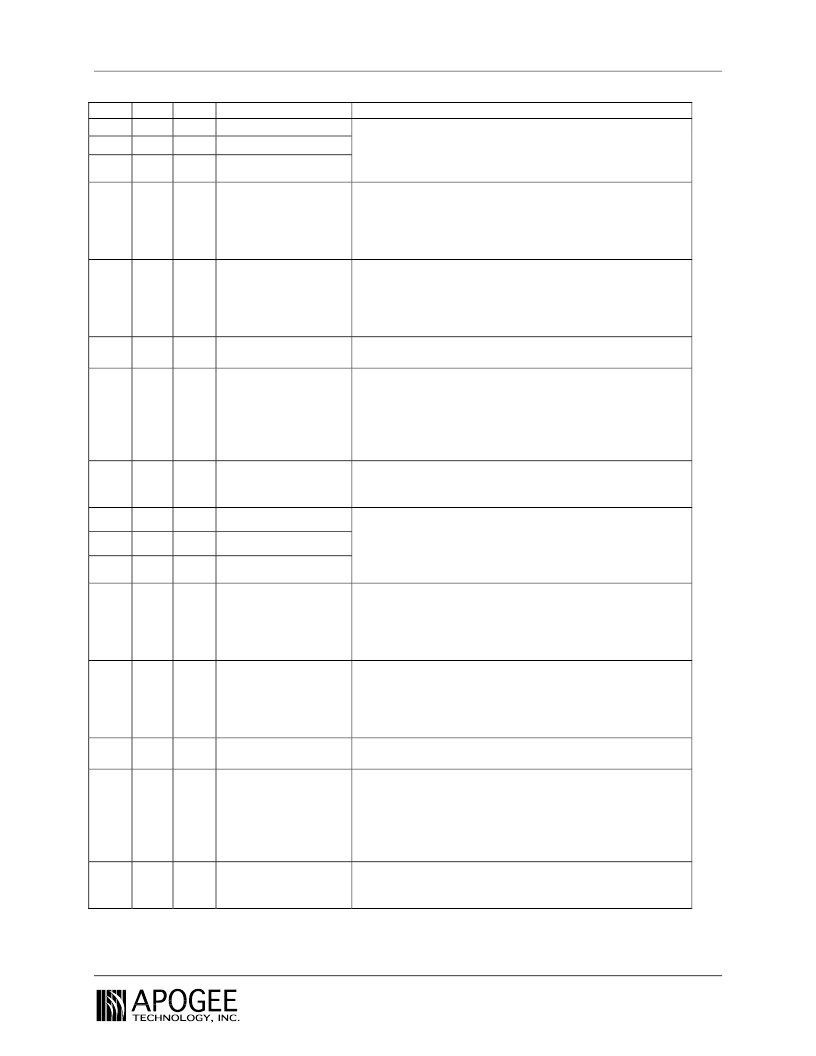

BIT

D0

D1

D2

R/W RST

R/W

R/W

R/W

NAME

I2SI_Align _0

I2SI_Align_1

I2SI_Align_2

DESCRIPTION

I

2

S (Input) Alignment. Using these bits the word

alignment can be adjusted with respect to the LRCK

edges. Please refer to the related paragraph for more

details. The default value is mode 1.

I

2

S (Input) BICK Polarity. This bit should be configured

according to the serial protocol used. In order to

sample incoming data on the rising edge (data

changes on the falling edge) this bit should be set to 1.

Set to 0 to reverse the sampling edge.

I

2

S (Input) Master/Slave Selection. The I

2

S input

interface can be configured as either master or slave:

if the master mode is selected (1) the BICK line will be

an output (64 x 48KHz fixed). Otherwise (0) slave

mode is selected and this line is an input.

I

2

S (Input) LRCK Polarity. Set to 0 to receive LEFT

samples when LRCK is low, 1 otherwise

I

2

S (Input) Master/Slave Selection. The I

2

S input

interface can be configured as either master or slave:

if the master mode is selected (1) the LRCK line will be

an output (48KHz fixed). Otherwise (0) slave mode is

selected and this line is an input (continuous frequency

between 32KHz and 96KHz).

I

2

S (Input) MSb/LSb Selection. Use this bit to select

how the sample word is received by the I

2

S input

interface: set to 0 to configure as LSb first, 1 MSb first.

I

2

S (Output) Alignment. Using these bits the word

alignment can be adjusted with respect to the LRCK

edges. The default value is mode 1.

1

0

0

D3

R/W

1

I2SI_BICK_Pol

D4

R/W

0

I2SI_BCK_Master

D5

R/W

0

I2SI_LRCK_Pol

D6

R/W

0

I2SI_LRCK_Master

D7

R/W

1

I2SO_MSbLSb

D8

R/W

1

I2SO_Align_0

D9

R/W

0

I2SO_Align_1

D10

R/W

0

I2SO_Align_2

D11

R/W

1

I2SO_BICK_Pol

I

2

S (Output) BICK Polarity. This bit should be

configured according to the used serial protocol. In

order to sample out coming data on the rising edge

(data changes on the falling edge) this bit should be

set to 1. Set to 0 to reverse the sampling edge.

I

2

S (Output) Master/Slave Selection. The I

2

S output

interface can be configured as either master or slave:

if the master mode is selected (1) the BICK line will be

an output (64 x 48kHz). Otherwise (0) slave mode is

selected and this line is an input.

I

2

S (Output) LRCK Polarity. Set to 0 to transmit LEFT

samples when LRCK is low, 1 otherwise.

I

2

S (Output) Master/Slave Selection. The I

2

S output

interface can be configured as either master or slave: if

the master mode is selected (1) the LRCK line will be

an output. Otherwise (0) slave mode is selected and

this line is an input. In any case the frequency is fixed

at 48kHz

I

2

S (Output) MSb/LSb Selection. Use this bit to select

how the sample word is transmitted by the I

S output

interface: set to 0 to configure as LSb first 1, MSb first.

D12

R/W

1

I2SO_BCK_Master

D13 R/W

0

I2SO_LRCK_Pol

D14

R/W

1

I2SO_LRCK_Master

D15 R/W

1

I2SO_MSbLSB

NOTE: Power-on default values will configure serial input interface as I

2

S Slave and the output interface as I

2

S Master.

24

Details and Specifications are subject to change without notice

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| DDX4100ERRATA | DDX4100 Errata January 17 2002 |

| DDY-EJE-T2 | LED Colored Resin |

| DDY-EJE-T2U-1 | LED Colored Resin |

| DDY-EJE-U1 | LED Colored Resin |

| DDY-EJE-U2 | LED Colored Resin |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| DDX-50P-K87 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50P-K87 / 121551-1664 / D Sub |

| DDX-50S-0L2-A197-146 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-0L2-A197-146 / 121551-0013 / D SUB |

| DDX-50S-A191-A197 | 制造商:ITT Interconnect Solutions 功能描述:DDX-50S-A191-A197 / 121551-1804 / D Sub |

| DDX8000-TRAY | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

| DDX8001-13TR | 制造商:APOGEE TECHNOLOGY 功能描述:DDX 8 Channel Damped Ternary Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。